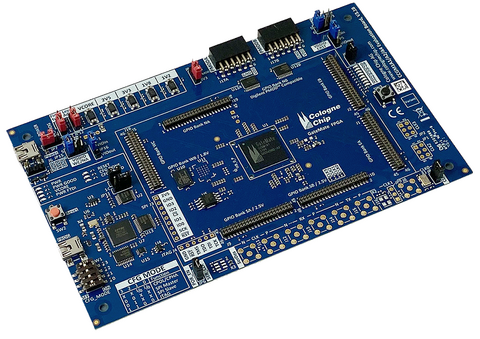

Main Features

GateMate A1 FPGA

- 20,480 programmable elements (each with 8-input LUT-tree, 2x FF/Latches, 2-bit full-adder or 2x2-bit multiplier)

- 0.9-1.1V core voltage, 1.2-2.5V I/O voltage

- 32 dual-port block RAM cells, total: 1,280 Kbit

- 4 configurable PLLs

- 2.5 Gbit/s SerDes

- all GPIO configurable as single-ended (total 162 signals) or LVDS differential pairs (total 81 pairs)

- all GPIO support double data rate (DDR)

- 324 balls 0.8 mm FPGA package, 15x15 mm

Interfaces

- USB-JTAG + USB-SPI configuration interface

- 2 Pmod-compatible ports

- SerDes interface via SMA

- 6 GPIO banks

Memory

- 64 Mbit Quad-I/O SPI flash @ 80 MHz

- 64 Mbit HyperRAM @ 166 MHz

- unpopulated footprint for secondary HyperRAM or HyerFlash module

Power

- Powered from USB

- adjustable Vcore (0.9-1.1V)

Dimensions

- 100x160 mm (Eurocard standard)