22/09/2023

GOWIN Is Offering the Andes A25 RISC-V CPU IP and AE350 SubsystemAs Instantiated Hard Cores in Its GW5AST-138 FPGA

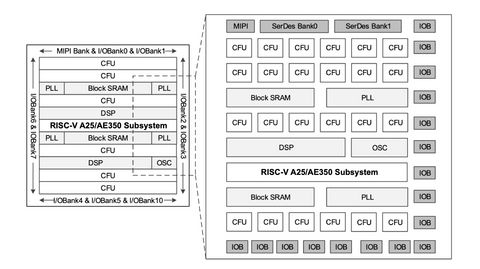

Andes Technology Corporation, a leading supplier of high efficiency, low-power 32/64-bit RISC-V processor cores and Founding Premier member of RISC-V International, is thrilled to announce that its AndesCore™ A25 RISC-V CPU IP and AE350 peripheral subsystem is hardened and embedded in the GW5AST-138 FPGA chip from GOWIN Semiconductor, the world’s fastest growing FPGA company. This integration, one of the first complete RISC-V microcontrollers in an FPGA, provides designers the A25 processor power and the peripherals most processors require without consuming any FPGA resources. Thus, the hardware team can populate the FPGA with their value-added design while the software team can concurrently create application code based on the rich RISC-V ecosystem.

In the Arora V family, the peripherals that a RISC-V CPU typically requires in hard instantiations are incorporated. Gowin included a fully controllable high-speed SerDes for communication, video aggregation, and AI computing acceleration applications that demand very high data rates. Other instantiated functions include Block RAM modules supporting ECC error correction, high-performance multiple voltage GPIO, and high accuracy clock architecture. These hard functions save the FPGA programmable fabric of up 138K LUT’s for the designers’ unique logic implementation.

The GW5AST-138 FPGA + Starter kit is available now from Alcom electronics.