## **DESCRIPTION**

The MP2672A is a highly integrated, flexible switch-mode battery charger IC for Lithium-ion batteries with two cells in series. This makes it applicable for a wide range of portable applications.

When an input power supply is present, the MP2672A operates in boost mode to charge the battery with two cells in series. When charging is enabled, the MP2672A automatically detects the battery voltage and charges the battery in three phases: pre-charge, constant current charge, and constant voltage charge. Other features include charge termination and auto-recharge.

The device also has a narrow voltage DC (NVDC) power structure. With a deeply discharged battery, the MP2672A regulates the system output to a minimum voltage level. This powers the system instantly while simultaneously charging the battery via the battery FET.

The MP2672A provides a cell balance function. It can monitor the voltage across each cell, then equalize the cell's voltages if the difference between the two cells exceeds the mismatch threshold.

The device has two configuration modes: standalone mode and host-control mode. In standalone mode, the charging parameters can be configured by hardware pins. In host-control mode, the charging parameters can configured by the I<sup>2</sup>C registers.

Diverse and robust protections include a thermal regulation loop to decrease the charge current in case the junction temperature exceeds the thermal loop threshold, and battery temperature protection that is compliant with JEITA standards. Other safety features include input over-voltage battery protection (OVP), OVP, thermal shutdown, battery temperature monitoring, a watchdog timer, and a configurable backup timer to prevent prolonged charging of a dead battery.

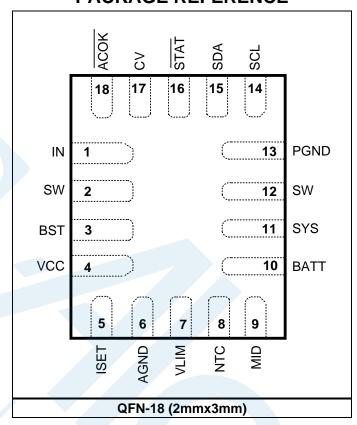

The MP2672A is available in a QFN-18 (2mmx3mm) package.

# MP2672A

## **Boost Charger with Cell Balance for** 2-Cell Lithium-Ion Batteries in Series

## **FEATURES**

- 4.0V to 5.75V Operating Input Voltage

- Up to 14V Sustainable Voltage

- Up to 2A Configurable Charge Current for Battery with 2 Cells in Series

- Compatible with Host-Control or Standalone Mode

- **NVDC Power Path Management**

- Configurable Input Voltage Limit

- Configurable Charge Voltage with 0.5% Accuracy

- No External Sense Resistor Required

- Integrated Cell-Balancing Circuit for Mismatched Cells

- Preconditioning for Fully Depleted Battery

- Flexible New Charging Cycle Initiation

- Charging Operation Indicator in Standalone Mode

- Missing Battery Detection in Host-Control

- I<sup>2</sup>C Port for Flexible System Parameter Setting and Status Reporting in Host-Control Mode

- Negative Temperature Coefficient (NTC) Pin for Temperature Monitoring Compliant with JEITA Standards

- **Built-In Charging Protection and** Configurable Safety Timer

- MOSFET Cycle-by-Cycle Over-Current Protection (OCP)

- Thermal Regulation and Thermal Shutdown

- Available in a QFN-18 (2mmx3mm) Package

#### **APPLICATIONS**

- Portable Handheld Solutions

- Point-of-Sale (POS) Machines

- **Bluetooth Speakers**

- E-Cigarettes

- **General 2-Cell Applications**

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

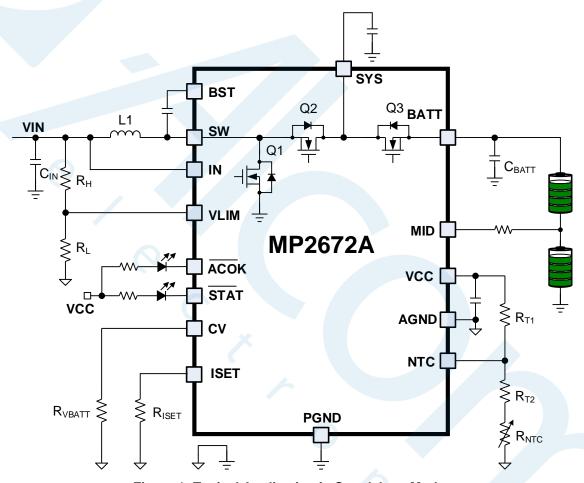

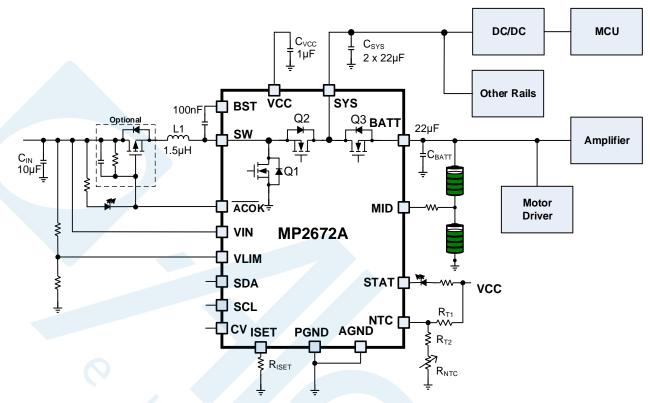

## **TYPICAL APPLICATIONS**

#### **Standalone Mode**

Use a resistor to connect the CV pin to AGND. Set the battery-full voltage according to Table 1.

**Table 1: Battery Voltage Settings**

| R <sub>VBATT</sub> Range | $V_{BATT\_REG}$ |

|--------------------------|-----------------|

| 30kΩ to 35kΩ             | 8.4V            |

| 70kΩ to 75kΩ             | 8.6V            |

| 100kΩ to 105kΩ           | 8.7V            |

| 130kΩ to 135kΩ           | 8.8V            |

Figure 1: Typical Application in Standalone Mode

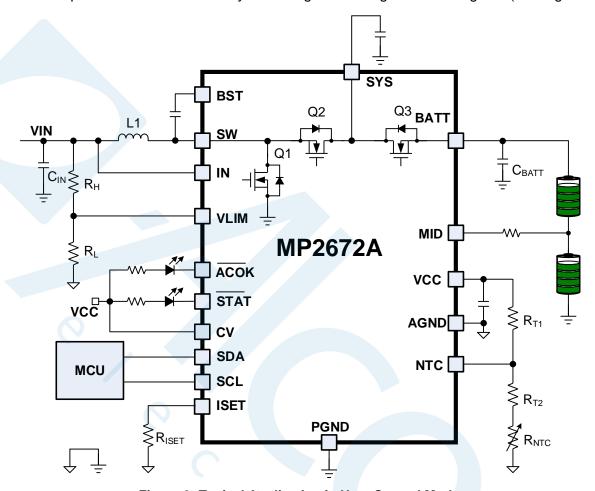

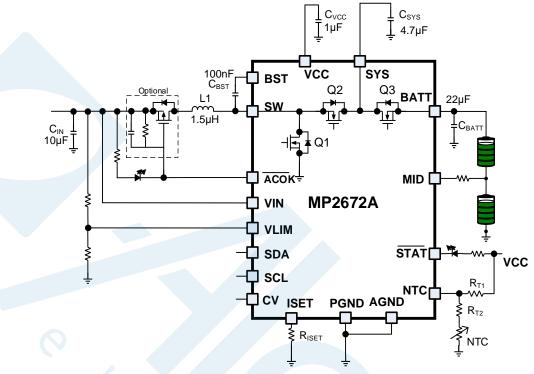

## **TYPICAL APPLICATIONS** (continued)

#### **Host-Control Mode**

Connect the CV pin to VCC. Set the battery-full voltage according to the I<sup>2</sup>C register (see Figure 2).

Figure 2: Typical Application in Host Control Mode

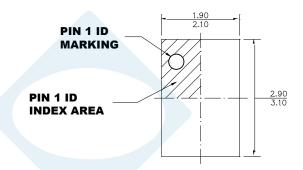

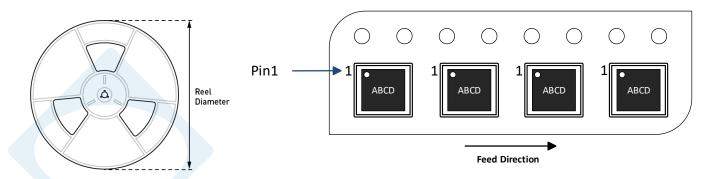

## ORDERING INFORMATION

| Part Number*     | Package          | Top Marking | MSL Rating |

|------------------|------------------|-------------|------------|

| MP2672AGD-xxxx** | QFN-18 (2mmx3mm) | See Below   | 1          |

| EVKT-MP2672A     | Evaluation kit   | N/A         | N/A        |

<sup>\*</sup>For Tape & Reel, add suffix –Z (e.g. MP2672AGD–xxxx–Z).

\*\*"-xxxx" is the register setting option. The factory default is "-0000". This content can be viewed in the I<sup>2</sup>C Register Map section starting on page 28. For custom options, contact an MPS FAE to obtain an "-xxxx" value.

### **TOP MARKING**

BNJ YWW

BNJ: Product code Y: Year code WW: Week code LLLL: Lot number

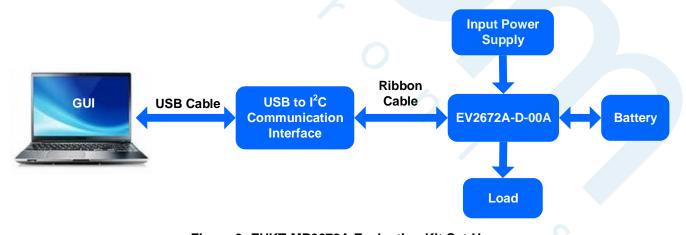

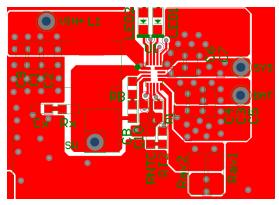

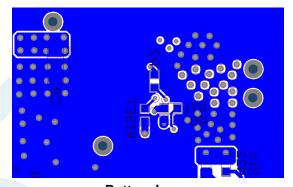

#### **EVALUATION KIT EVKT-MP2672A**

EVKT-MP2672A kit contents (items below can be ordered separately):

| # | Part Number        | Item                                                                                    | Quantity |

|---|--------------------|-----------------------------------------------------------------------------------------|----------|

| 1 | EV2672A-D-00A      | MP2672A evaluation board                                                                | 1        |

| 2 | EVKT-USBI2C-02 bag | Includes one USB to $I^2C$ communication interface, one USB cable, and one ribbon cable | 1        |

| 3 | Online resources   | Include datasheet, user guide, product brief, and GUI                                   | 1        |

## Order directly from MonolithicPower.com or our distributors.

Figure 3: EVKT-MP2672A Evaluation Kit Set-Up

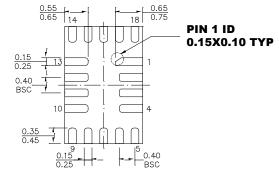

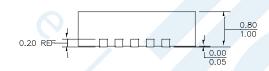

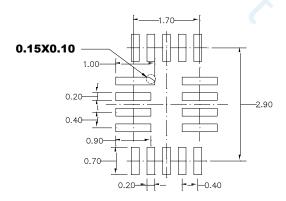

## **PACKAGE REFERENCE**

## **PIN FUNCTIONS**

| Pin # | Name | Type (1) | Description                                                                                                                                                                                                                                                                                                                             |

|-------|------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | IN   | Р        | Input power pin.                                                                                                                                                                                                                                                                                                                        |

| 2, 12 | SW   | Р        | <b>Switching node.</b> The SW pin is the middle point between the MP2672A's high-side and low-side MOSFETs.                                                                                                                                                                                                                             |

| 3     | BST  | Р        | <b>Bootstrap.</b> Connect a bootstrap capacitor between the BST and SW pins to provide a floating supply for the high-side FET driver.                                                                                                                                                                                                  |

| 4     | VCC  | Р        | Internal LDO output pin. Bypass a 1µF ceramic capacitor from this pin to AGND. It is not recommended to pull more than 20mA from this pin.                                                                                                                                                                                              |

| 5     | ISET | Al       | <b>Charge current setting.</b> Connect an external resistor from this pin to AGND to configure the charge current. This also limits the maximum charge current in host-control mode.                                                                                                                                                    |

| 6     | AGND | Р        | Analog ground.                                                                                                                                                                                                                                                                                                                          |

| 7     | VLIM | Al       | <b>Input voltage limit feedback pin.</b> Connect a resistor divider from IN to AGND to configure the minimum input voltage limit threshold.                                                                                                                                                                                             |

| 8     | NTC  | AI       | Battery temperature-sense input. Connect NTC to a negative temperature coefficient thermistor. Configure the temperature window with a voltage divider connected from VRNTC to NTC to AGND. Configurable JEITA thresholds are supported. See the Negative Temperature Coefficient (NTC) Thermistor section on page 23 for more details. |

| 9     | MID  | Р        | <b>Middle point of the high-side and low-side cells.</b> The MID pin measures the voltage of each cell and provides a balance path for each cell. Connect MID to AGND to disable the cell balance function.                                                                                                                             |

| 10    | BATT | Р        | <b>Battery positive terminal.</b> Connect a capacitor from BATT to PGND, and place it as close as possible to the IC.                                                                                                                                                                                                                   |

| 11    | SYS  | Р        | <b>System output.</b> Connect a capacitor from SYS to PGND, and place it as close as possible to the IC.                                                                                                                                                                                                                                |

| 13    | PGND | Р        | Power ground.                                                                                                                                                                                                                                                                                                                           |

| 14    | SCL  | DI       | I <sup>2</sup> C interface clock pin. This pin is only valid if the CV pin is connected to VCC.                                                                                                                                                                                                                                         |

| 15    | SDA  | DIO      | I <sup>2</sup> C interface data pin. This pin is only valid if the CV pin is connected to VCC.                                                                                                                                                                                                                                          |

| 16    | STAT | DO       | Charging operation indicator. This pin is an open-drain output.                                                                                                                                                                                                                                                                         |

| 17    | CV   | AI       | <b>Operation mode and battery voltage control pin.</b> Pull CV to VCC to configure the IC to host-control mode. Connect an external resistor to AGND to configure IC to standalone mode. In standalone mode, configure the battery-full voltage via the CV pin's resistor.                                                              |

| 18    | ACOK | DO       | <b>Valid input supply indicator.</b> This pin is an open-drain output. It is pulled low when the input voltage exceeds the under-voltage lockout threshold ( $V_{IN\_UVLO}$ ) and is below the over-voltage lockout threshold ( $V_{IN\_OVLO}$ ).                                                                                       |

#### Note:

1) Al = analog input, Dl = digital input, DO = digital output, DlO = digital input and output, P = power.

| ABSOLUTE MAXIMUM RATINGS (2)                            |

|---------------------------------------------------------|

| BATT0.3V to +14V                                        |

| SW0.3V (-2V for 50ns) to +14V                           |

| SYS0.3V to +14V                                         |

| MID, IN0.3V to +12V                                     |

| BST to SW0.3V to +5V                                    |

| All other pins to AGND0.3V to +5V                       |

| Continuous power dissipation(T <sub>A</sub> = 25°C) (3) |

| 1.78W                                                   |

| Junction temperature150°C                               |

| Lead temperature (solder)260°C                          |

| Storage temperature65°C to +150°C                       |

| ESD Ratings                                             |

| Human body model (HBM) (5) 2000V                        |

| Charged device model (CDM) (6) 250V                     |

| Recommended Operating Conditions (4)                    |

| IN to PGND                                              |

| BATT to PGNDUp to 9V                                    |

| I <sub>CC</sub> Up to 2A                                |

| I <sub>DSCHG</sub> Up to 3A                             |

| I <sub>SYS</sub> Up to 2A                               |

Operating junction temp (T<sub>J</sub>).... -40°C to +125°C

| Thermal Resistance (7) | $oldsymbol{	heta}_{JA}$ | $\boldsymbol{\theta}$ JC |      |

|------------------------|-------------------------|--------------------------|------|

| QFN-18 (2mmx3mm)       | 70                      | 15                       | °C/W |

#### Notes:

- 2) Exceeding these ratings may damage the device.

- 3) The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_J$  (MAX), the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)  $T_A$ ) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can cause excessive die temperature, and the regulator may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 5) Per ANSI/ESDA/JEDEC JS-001.

- 6) Per JESD22-C101.

- 7) Measured on JESD51-7, 4-layer PCB.

© 2020 MPS. All Rights Reserved.

## **ELECTRICAL CHARACTERISTICS**

$V_{IN} = 5V$ ,  $T_A = 25$ °C, unless otherwise noted.

| Parameter                                               | Symbol                | Condition                                          | Min  | Тур  | Max  | Units |

|---------------------------------------------------------|-----------------------|----------------------------------------------------|------|------|------|-------|

| Input Power Characteristics                             |                       |                                                    |      |      |      |       |

| Input over-voltage lockout (OVLO) threshold             | V <sub>IN_OVLO</sub>  | V <sub>IN</sub> rising                             | 5.75 | 6.0  | 6.25 | V     |

| Input OVLO threshold hysteresis                         |                       |                                                    |      | 150  |      | mV    |

| Input under-voltage lockout (UVLO) threshold            | VIN_UVLO              | V <sub>IN</sub> falling                            | 3.25 | 3.45 | 3.65 | V     |

| Input UVLO threshold hysteresis                         |                       |                                                    |      | 150  |      | mV    |

| Boost Converter                                         |                       |                                                    |      |      |      |       |

| VCC LDO output                                          | Vvcc                  | V <sub>IN</sub> = 5V, I <sub>VCC</sub> = 20mA      | 3.5  | 3.6  | 3.7  | V     |

| Low-side N-channel MOSFET on resistance                 | R <sub>ON_Q1</sub>    |                                                    |      | 54   | 70   | mΩ    |

| High-side N-channel MOSFET on resistance                | R <sub>ON_Q2</sub>    |                                                    |      | 28   | 40   | mΩ    |

| Peak current limit for low-side N-channel MOSFET        | I <sub>LS_PK</sub>    | V <sub>IN</sub> =5V                                | 6    | 7    |      | Α     |

| Valley current limit for high-<br>side N-channel MOSFET | IHS_VL                | V <sub>IN</sub> =5V                                | 5    | 6    |      | Α     |

| Operating frequency                                     | f <sub>SW</sub>       | REG07H, bit[7] = 1                                 | 1100 | 1270 | 1440 | kHz   |

| System regulation minimum voltage (VBATT_PRE + VTRACK)  |                       | REG00H, bits[3:1] = 100,<br>V <sub>BATT</sub> = 5V | 6.55 | 6.7  | 6.85 | V     |

| Battery track regulation voltage                        | VTRACK                |                                                    |      | 300  |      | mV    |

| Battery Charger                                         |                       |                                                    |      |      |      |       |

|                                                         |                       | REG00H, bits[3:1] = 000                            | 5.9  | 6.05 | 6.2  |       |

| Pre-charge threshold                                    | V <sub>BATT_PRE</sub> | REG00H, bits[3:1] = 100                            | 6.25 | 6.4  | 6.55 | V     |

|                                                         |                       | REG00H, bits[3:1] = 111                            | 6.6  | 6.75 | 6.9  |       |

| Pre-charge threshold hysteresis                         |                       | V <sub>BATT</sub> falling                          |      | 250  |      | mV    |

| Pre-charge current                                      | I <sub>PRE</sub>      | V <sub>BATT</sub> = 5.9V                           | 230  | 320  | 410  | mA    |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN} = 5V$ ,  $T_A = 25$ °C, unless otherwise noted.

| Parameter                                            | Symbol              | Condition                                                                                                      | Min   | Тур | Max   | Units |

|------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------|-------|-----|-------|-------|

| Fact charge current                                  | pet charge current  |                                                                                                                | 0.9   | 1   | 1.1   | А     |

| Fast charge current                                  | Icc                 | REG01H, bits[3:0] = 1111,<br>R <sub>ISET</sub> = $6k\Omega$                                                    | 1.8   | 2   | 2.2   | А     |

| Termination charge current                           | I <sub>TERM</sub>   | If I <sub>CC</sub> > 1.5A, as a percentage of I <sub>CC</sub>                                                  | 8     | 11  | 14    | %     |

|                                                      |                     | If I <sub>CC</sub> ≤ 1.5A (setting)                                                                            | 130   | 160 | 190   | mA    |

| Input minimum voltage regulation reference           | VIN_MIN_REF         |                                                                                                                | 1.18  | 1.2 | 1.22  | V     |

|                                                      |                     | V <sub>BATT_REG</sub> = 8.3V, host-control mode, REG00H, bits[7:5] = 000                                       |       |     |       |       |

| Battery charge voltage                               | V                   | $V_{BATT\_REG} = 8.4V$ , host-control mode: REG00H, bits[7:5] = 001, standalone mode: $R_{VBATT} = 30k\Omega$  | -0.50 |     | +0.50 | %     |

| regulation                                           | VBATT_REG_ACC       | $V_{BATT\_REG} = 8.8V$ , host-control mode: REG00H, bits[7:5] = 101, standalone mode: $R_{VBATT} = 135k\Omega$ | -0.50 |     |       |       |

|                                                      |                     | V <sub>BATT_REG</sub> = 8.2V, host-control mode, REG00H, bits[7:5] = 111                                       |       |     |       |       |

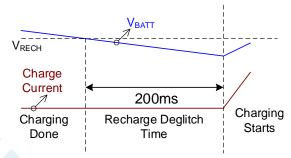

| Recharge threshold below VBATT_REG                   | V <sub>RECH</sub>   |                                                                                                                |       | 450 |       | mV    |

| Battery pack over-voltage protection (OVP) threshold | VBATT_OVP           | As a percentage of VBATT_REG                                                                                   | 102   | 104 | 105   | %     |

| Battery pack OVP hysteresis                          |                     | REG00H, bit[0] = 0                                                                                             |       | 150 |       | mV    |

| SYS-to-BATT N-channel MOSFET on resistance           | R <sub>ON_Q3</sub>  |                                                                                                                | 22    | 31  | 40    | mΩ    |

| Battery quiescent current                            | I <sub>BATT_Q</sub> | $V_{IN} < V_{IN\_UVLO}, V_{BATT} = 8.4V,$ system no load                                                       | 19    | 31  | 42    | μΑ    |

| ACOK, STAT, pin output low voltage                   |                     | Sinking 1.5mA                                                                                                  |       |     | 400   | mV    |

| ACOK, STAT, pin leakage current                      |                     | Connected to 5V                                                                                                |       |     | 1     | μΑ    |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN} = 5V$ ,  $T_A = 25$ °C, unless otherwise noted.

| Parameter                                                   | Symbol                     | Condition                                            | Min  | Тур   | Max  | Units |

|-------------------------------------------------------------|----------------------------|------------------------------------------------------|------|-------|------|-------|

| Termination deglitch time                                   | tterm_dgl                  |                                                      |      | 180   |      | ms    |

| Recharge deglitch time                                      | trech_dgl                  |                                                      |      | 180   |      | ms    |

| <b>Battery Temperature Monitori</b>                         | ng (JEITA)                 |                                                      |      |       |      |       |

| NTC low temp rising threshold                               | Vcold                      | As a percentage of Vcc                               | 70   | 71    | 72   | %     |

| NTC low temp rising threshold hysteresis                    |                            | As a percentage of Vcc                               |      | 2.4   |      | %     |

| NTC cool temp rising threshold                              | V <sub>COOL</sub>          | As a percentage of V <sub>CC</sub>                   | 62   | 63    | 64   | %     |

| NTC cool temp rising threshold hysteresis                   |                            | As a percentage of V <sub>CC</sub>                   |      | 2.2   |      | %     |

| NTC warm temp falling threshold                             | Vwarm                      | As a percentage of Vcc                               | 39.4 | 40.4  | 41.4 | %     |

| NTC warm temp falling threshold hysteresis                  |                            | As a percentage of Vcc                               |      | 2.5   |      | %     |

| NTC hot temp falling threshold                              | V <sub>НОТ</sub>           | As a percentage of Vcc                               | 33.5 | 34.5  | 35.5 | %     |

| NTC hot temp falling threshold hysteresis                   |                            | As a percentage of Vcc                               |      | 2.5   |      | %     |

| Thermal Regulation and Prote                                | ection                     |                                                      |      |       |      |       |

| Thermal shutdown temperature                                | T <sub>J_SHDN</sub>        | Rising threshold                                     |      | 150   |      | °C    |

| Thermal shutdown hysteresis                                 |                            | Temperature falling                                  |      | 20    |      | °C    |

| Cell Balance Function                                       |                            |                                                      |      |       |      |       |

| Internal balance FET on                                     | R <sub>ON_BHS</sub>        |                                                      |      | 2.1   |      | Ω     |

| resistance                                                  | R <sub>ON_BLS</sub>        |                                                      |      | 1.3   |      | Ω     |

| Cell balance starting voltage threshold                     | Vcell_bal                  | l <sup>2</sup> C-configurable,<br>REG01H, bit[6] = 0 | 3.35 | 3.5   | 3.65 | V     |

| Cell voltage high-to-low cell mismatch threshold            | V <sub>CELL_DIFF_HTL</sub> | REG01H, bit[5] = 0                                   |      | 50    | 70   | mV    |

| Cell voltage high-to-low cell mismatch threshold hysteresis |                            |                                                      |      | 52    |      | mV    |

| Cell voltage low-to-high cell mismatch threshold            | VCELL_DIFF_LTH             | REG01H, bit[4] = 0                                   |      | 50    | 70   | mV    |

| Cell voltage low-to-high cell mismatch threshold hysteresis |                            | 0                                                    |      | 58    |      | mV    |

| High-side cell OVP threshold                                | VHCELL_OVP                 | As a percentage of the battery-full voltage          | 101  | 102.5 | 104  | %     |

| Low-side OVP threshold                                      | V <sub>LCELL_OVP</sub>     | As a percentage of the battery-full voltage          | 101  | 102.5 | 104  | %     |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN} = 5V$ ,  $T_A = 25$ °C, unless otherwise noted.

| Parameter                                | Symbol                  | Condition                                                | Min | Тур | Max | Units |

|------------------------------------------|-------------------------|----------------------------------------------------------|-----|-----|-----|-------|

| I <sup>2</sup> C Communication Interface |                         |                                                          |     |     |     |       |

| Input high threshold level               | ViH                     | VPULL UP = 1.8V                                          | 1.3 |     |     | V     |

| Input low threshold level                | VıL                     | V <sub>PULL_UP</sub> = 1.8V                              |     |     | 0.4 | V     |

| Output low threshold level               | Vol                     | Isink = 5mA                                              |     |     | 0.4 | V     |

| I <sup>2</sup> C clock frequency         | f <sub>SCL</sub>        |                                                          |     |     | 400 | kHz   |

| Timing Characteristics                   |                         |                                                          |     |     |     |       |

| Clock frequency                          | fclk                    |                                                          |     | 131 |     | kHz   |

| Watchdog timer <sup>(8)</sup>            | twtd                    | REG02H, bits[5:4] = 01                                   |     | 40  |     | sec   |

| Safety charge timer                      | <b>t</b> <sub>TMR</sub> | I <sup>2</sup> C-configurable,<br>REG02H, bits[2:1] = 11 | 16  | 20  |     | hours |

| Pre-charge timer                         |                         |                                                          |     | 1   |     | hours |

#### Note:

11/10/2020

8) Guaranteed by design

11

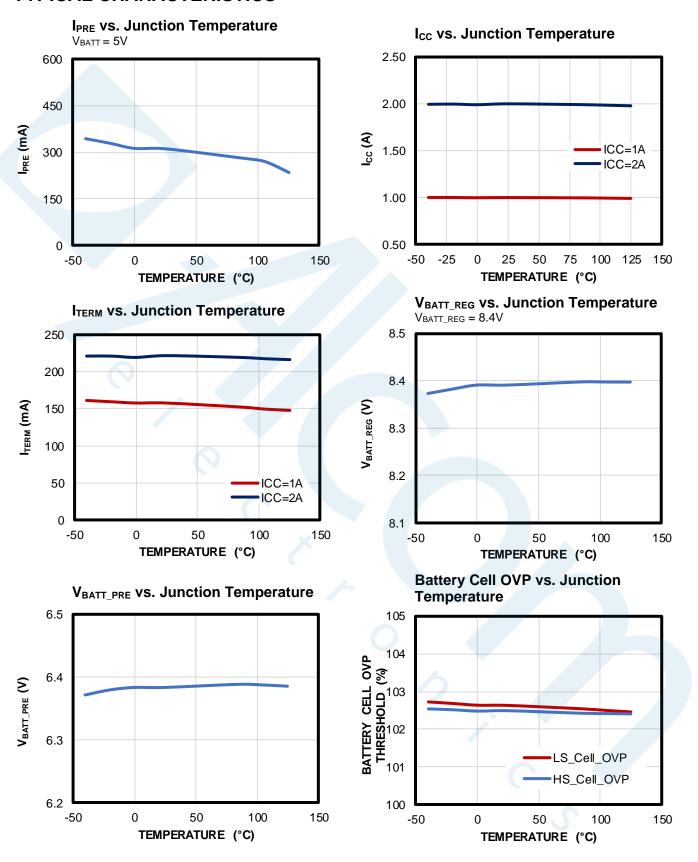

### TYPICAL CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN} = 5V$ ,  $T_A = 25$ °C, unless otherwise noted.

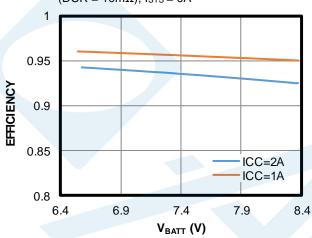

# **Constant Current Mode Charge Efficiency**

$V_{IN}=5V$ ,  $f_{SW}=1200kHz$ ,  $L=1.5\mu H$ , (DCR =  $10m\Omega$ ),  $I_{SYS}=0A$

# **Constant Voltage Mode Charge Efficiency**

$V_{IN} = 5V$ ,  $f_{SW} = 1200kHz$ ,  $L = 1.5\mu H$ , (DCR =  $10m\Omega$ ),  $V_{BATT} = 8.4V$ ,  $I_{SYS} = 0A$

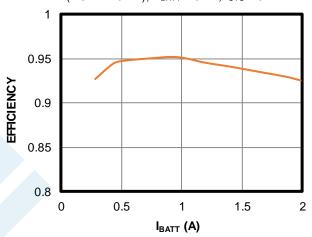

## **Configurable Charge Current**

Standalone mode

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

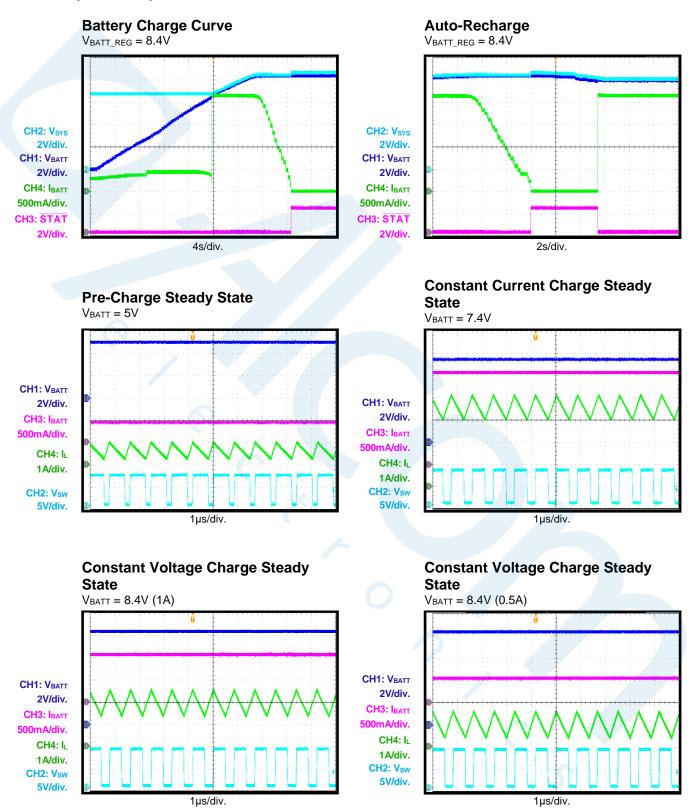

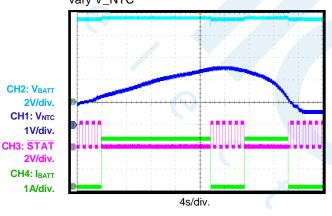

$V_{IN}=5V,~V_{BATT\_PRE}=6.5V,~I_{CC}=2A,~I_{SYS}=0A,~V_{BATT}=0V~to~8.4V,~C_{IN}=10\mu F,~C_{SYS}=44\mu F,~C_{BATT}=22\mu F,~L=1.5\mu H,~f_{SW}=1200kHz,~T_A=25^{\circ}C,~unless~otherwise~noted.$

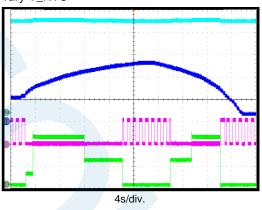

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

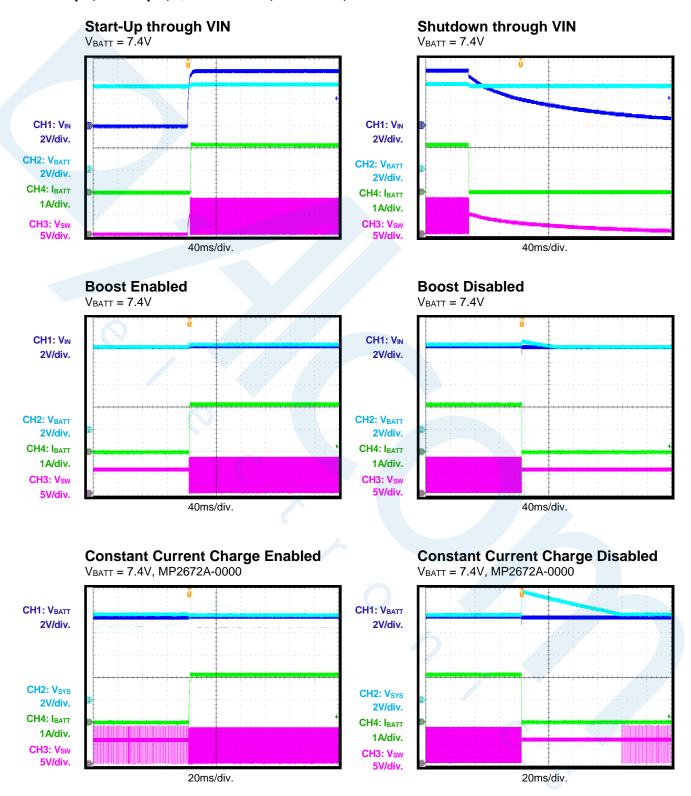

$V_{IN} = 5V$ ,  $V_{BATT\_PRE} = 6.5V$ ,  $I_{CC} = 2A$ ,  $I_{SYS} = 0A$ ,  $V_{BATT} = 0V$  to 8.4V,  $C_{IN} = 10\mu F$ ,  $C_{SYS} = 44\mu F$ ,  $C_{BATT} = 22\mu F$ ,  $L = 1.5\mu H$ ,  $f_{SW} = 1200kHz$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

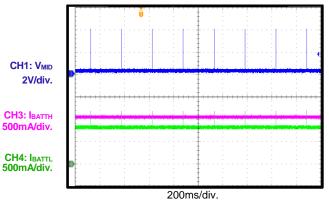

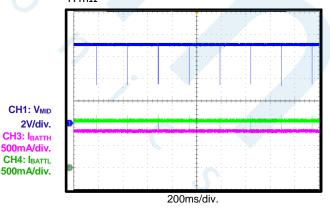

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

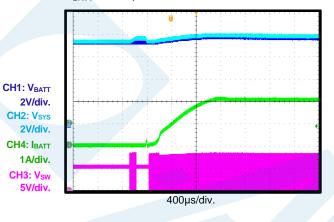

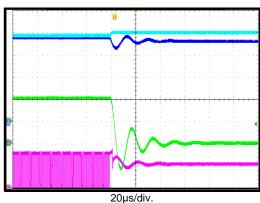

$V_{IN} = 5V$ ,  $V_{BATT} = 0V$  to 8.4V,  $C_{IN} = 10\mu F$ ,  $C_{SYS} = 44\mu F$ ,  $C_{BATT} = 22\mu F$ ,  $L = 1.5\mu H$ ,  $f_{SW} = 1200 kHz$ ,  $T_A = 25$ °C, unless otherwise noted.

CH1: VBATT

CH2: V<sub>SYS</sub>

CH4: IBATT

CH3: V<sub>SW</sub>

CH2: VBATT

CH1: V<sub>NTC</sub>

2V/div.

1V/div.

**CH3:**

STAT

2V/div.

1A/div.

CH4: I<sub>BATT</sub>

2V/div.

2V/div.

1A/div.

5V/div.

## **Constant Current Charge Enabled**

$V_{BATT} = 7.4V, MP2672A-000E$

## **Constant Current Charge Disabled**

V<sub>BATT</sub> = 7.4V, MP2672A-000E

#### **Standard NTC Protection**

$V_{BATT} = 7.4V$ , standard NTC,  $I_{CC} = 2A$ , vary V\_NTC

#### **JEITA NTC Protection**

V<sub>BATT</sub> = 8.15V, JEITA NTC, I<sub>CC</sub> = 2A, vary V\_NTC

#### LS Cell Balance

Icc = 1A, Isys = 0A, HS cell is 3.6V and LS cell is 3.8V, balance enabled, balance resistor is  $17m\Omega$

#### **HS Cell Balance**

Icc = 1A, Isys = 0A, HS cell is 3.8V and LS cell is 3.6V, balance enabled, balance resistor is  $17 m \Omega\,$

© 2020 MPS. All Rights Reserved.

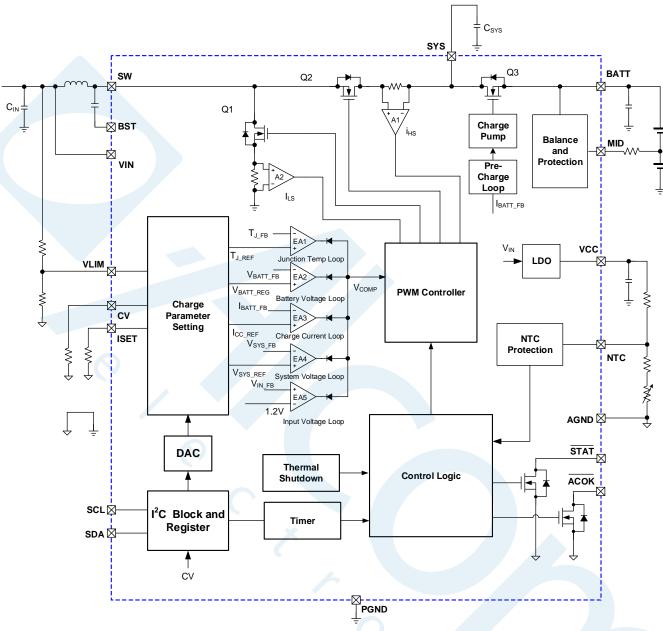

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 4: Functional Block Diagram

#### **OPERATION**

The MP2672A is a highly integrated switchmode battery charger IC that charges lithium-ion batteries with two cells in series from a 5V input power supply. This means it can be used with an adapter or USB input.

#### **Host-Control Mode and Standalone Mode**

The MP2672A can operate in either host-control mode or standalone mode. After the input starts up, the MP2672A checks the CV pin's status.

If CV is pulled up to logic high, the MP2672A works in host-control mode. If CV is connected to ground through a resistor, the MP2672A works in standalone mode.

In host-control mode, the charging parameters ( $V_{BATT\_REG}$  and  $I_{CC}$ ) can be configured by the  $I^2C$  registers. In standalone mode, they can be set by hardware pins.

Table 2: Host-Control Mode vs. Standalone Mode

| CV Pin                         | Mode             | V <sub>BATT_REG</sub>                  | Icc                                                   |

|--------------------------------|------------------|----------------------------------------|-------------------------------------------------------|

| Connected to AGND via resistor | Standalone       | Set by<br>CV<br>resistor               | Set by<br>ISET<br>resistor                            |

| Pulled up<br>to VCC            | Host-<br>control | Set by<br>I <sup>2</sup> C<br>register | Set by<br>I <sup>2</sup> C<br>register <sup>(9)</sup> |

#### Note:

#### **Internal Power Supply**

The VCC LDO is powered by the input power supply, and it powers the internal circuit and MOSFET driver. When the input is absent, the VCC LDO is off. An external capacitor must be connected from the VCC pin to AGND. The VCC output is regulated to about 3.6V when  $V_{\rm IN}$  is 5V. If  $V_{\rm IN}$  is below 3.6V, the LDO enters low-dropout mode, and the LDO FET fully turns on. The VCC output cannot handle current loads exceeding 20mA.

## Input Voltage vs. System Voltage Limitation

To prevent the MP2672A from entering open-loop operation due to the low-side MOSFET's minimum on time, the boost converter turns off if Vsys drops below 110% of  $V_{\rm IN}$ . The converter restarts, then checks the input voltage and system voltage again.

The boost converter turns off again if  $V_{SYS}$  is still below 110% of  $V_{IN}$  after a 1ms soft-start time.

It is recommended to choose  $V_{\text{BATT\_PRE}}$  and  $V_{\text{TRACK}}$  to ensure that the minimum output voltage of the boost converter exceeds 110% of the maximum DC input voltage.

#### **Input Power Start-Up**

When the input voltage is below the undervoltage lockout threshold ( $V_{\text{IN\_UVLO}}$ ), SYS is powered by the battery via Q3, which is fully turned on at this time. When input power is connected and  $V_{\text{IN}}$  exceeds  $V_{\text{IN\_UVLO}}$ , Q3 stops being fully on and enters virtual diode mode. At the same time, the boost converter starts up with a soft start of the system voltage loop. When the system voltage rises to about 20mV above the battery voltage, Q3 turns off. It turns on again with a soft-start charging current after the system's voltage soft start completes.

### Narrow Voltage DC (NVDC) Power Structure

The MP2672A features a narrow voltage DC (NVDC) power structure that is comprised of a frond-end boost converter and a rear-end battery FET between the SYS and BATT pins. This allows for separate control between the system and the battery. The system is given the priority to start up, even with a deeply discharged or missing battery. When input power is available and a depleted battery is connected, the system voltage is regulated to the minimum system voltage (V<sub>SYS\_MIN</sub>) which is set via REG00H, bits[3:1].

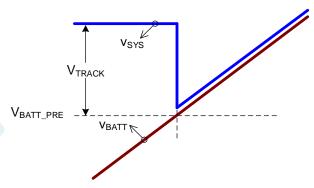

Figure 5 shows the system voltage control, described in detail below:

- When the battery voltage (VBATT) is below VBATT\_PRE, the system voltage is regulated to VSYS\_REG\_MIN = VBATT\_PRE + VTRACK. The battery FET works linearly to charge the battery with the pre-charge current.

- When V<sub>BATT</sub> is above V<sub>BATT\_PRE</sub>, the battery FET is fully turned on, and the system voltage always exceeds V<sub>BATT</sub> by the value calculated with I<sub>BATT</sub> x R<sub>ON\_Q3</sub>. Once battery charging completes, the system output (V<sub>SYS</sub>) is regulated to V<sub>BATT</sub> + V<sub>TRACK</sub>.

The maximum charge current is limited by the ISET pin, even in host-control mode.

When charging is disabled and REG00H, bit[4] = 0, V<sub>SYS</sub> is also regulated to V<sub>TRACK</sub>, which is greater than the real battery voltage.

Figure 5: V<sub>SYS</sub> Variation with V<sub>BATT</sub>

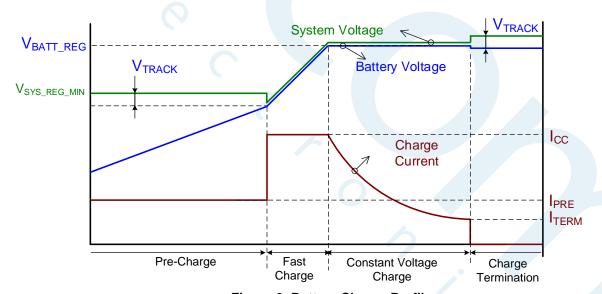

## **Battery Charge Profile**

The MP2672A provides three main charging phases: constant current pre-charge, constant current fast charge, and constant voltage charge (see Figure 6).

Phase 1 (Constant Current Pre-Charge): When VBATT is below the pre-charge to fast charge threshold (VBATT\_PRE), the MP2672A regulates the system voltage to VSYS\_REG\_MIN. The part applies a safe pre-charge current (IPRE) to charge the deeply depleted battery until VBATT reaches

V<sub>BATT\_PRE</sub>. If V<sub>BATT\_PRE</sub> is not reached before the pre-charge timer (60min) expires, the charge cycle ceases, and a corresponding timeout fault signal is asserted.

Phase 2 (Constant Current Fast Charge): When VBATT exceeds VBATT\_PRE, the MP2672A stops the pre-charge phase and enters the fast charge phase. The fast charge current can be configured via the ISET pin in standalone mode or via the I<sup>2</sup>C register in host-control mode.

Figure 6: Battery Charge Profile

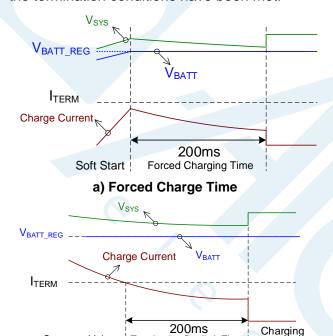

Phase 3 (Constant Voltage Charge): When V<sub>BATT</sub> reaches the battery regulation voltage (V<sub>BATT\_REG</sub>), the charge current begins to decrease (see Figure 7). The charge cycle is complete once the constant voltage loop is dominant, and the charge current drops below the charge termination current threshold for a 200ms deglitch time. This 200ms deglitch time is designed to start each charge cycle; after 200ms expires, the charge-full signal asserts whether the termination conditions have been met.

b) Termination Deglitch Time

Figure 7: Forced Charge Time and Termination

Deglitch Time

Done

Constant Voltage Termination Deglitch Time

If  $I_{\text{TERM}}$  is not reached before the safety charge timer expires (see the Safety Timer section on page 22), the charging cycle stops and the corresponding timeout fault signal is asserted.

Charging termination can be manually disabled by pulling the NTC pin up to VCC. A new charging cycle starts when the following conditions are valid:

- The input power is re-plugged in

- Auto-recharge is enabled

- The charging enable bit is toggled (only for host-control mode)

- There is no thermistor fault on the NTC pin

- There is no safety timer fault

- There is no battery over-voltage condition

- Thermal shutdown is not occurring

#### Auto-Recharge

When the battery is fully charged and charging is terminated, the battery may be discharged by system consumption or self-discharge (see Figure 8). The MP2672A automatically starts a new charging cycle (without requiring a manual charging cycle restart) when the battery voltage drops below the recharge threshold for 200ms.

Figure 8: Recharging Profile

### **Charging Enabled (Default Setting)**

If the battery is not expected to be charged frequently during high state of charge (SOC) conditions, the MP2672A has an one-time programmable (OTP) option (REG05H, bit[7]) to disable charging when the input power is on, and the battery voltage exceeds the recharge voltage threshold. Charging is enabled until the battery voltage falls below the recharge threshold.

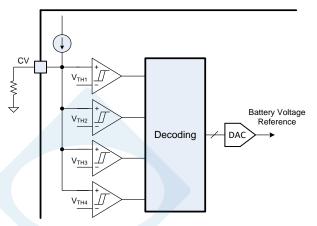

#### **Battery-Full Voltage Setting**

The MP2672A has a CV pin that can configure the battery regulation voltage.

When CV is pulled up to VCC, the MP2672A operates in host-control mode. The battery regulation voltage is configured through the I<sup>2</sup>C.

When CV is connected to AGND via a resistor, the MP2672A operates in standalone mode. The battery regulation voltage is set according to Table 3.

Table 3: VBATT\_REG vs. RVBATT Resistor

| Resistor Range             | $V_{BATT\_REG}$ |

|----------------------------|-----------------|

| 30kΩ to 35kΩ               | 8.4V            |

| $70k\Omega$ to $75k\Omega$ | 8.6V            |

| 100kΩ to 105kΩ             | 8.7V            |

| 130kΩ to 135kΩ             | 8.8V            |

Figure 9 shows the simplified diagram.

Figure 9: Simplified Diagram of the V<sub>BATT\_REG</sub> Setting in Standalone Mode

## **Charge Current Setting**

In standalone mode, the charge current ( $I_{CC}$ ) is set by a resistor connected to the ISET pin ( $R_{ISET}$ ). Calculate  $I_{CC}$  with Equation (1):

$$I_{CC} = \frac{12k\Omega}{R_{ISET}}(A)$$

(1)

In host-control mode, the charge current can be configured via  $R_{\text{ISET}}$  and REG01H, bits[3:0].  $R_{\text{ISET}}$  determines the full-scale value of the register. For example, if  $R_{\text{ISET}}$  is  $6k\Omega$ , the  $I^2C$ -configurable range is between 500mA and 2000mA, with 100mA per step. If  $R_{\text{ISET}}$  is  $24k\Omega$ , the  $I^2C$ -configurable range is between 125mA and 500mA, with 25mA per step.  $R_{\text{ISET}}$  is recommended to be between  $6k\Omega$  and  $24k\Omega$ .

#### **Minimum Input Voltage Limit**

To avoid overloading the adapter, the MP2672A implements input voltage based power management by continuously monitoring the input voltage ( $V_{IN}$ ). When the minimum input voltage limit ( $V_{IN\_MIN}$ ) is reached, the charge current is reduced to prevent  $V_{IN}$  from dropping further.  $V_{IN\_MIN}$  can be configured by a voltage divider on the VLIM pin.

The internal reference of the input voltage loop is 1.2V, and  $V_{\text{IN\_MIN}}$  can be estimated with Equation (2):

$$V_{IN\_MIN} = 1.2 \times \frac{R_H + R_L}{R_L}$$

(2)

# **Battery Supplement Mode and Virtual Diode Mode**

When  $V_{\text{IN\_MIN}}$  is reached, the charge current is reduced to keep  $V_{\text{IN}}$  from dropping further. However, if the charge current drops to 0A and the input source is still overloaded due to a heavy system load, the system voltage ( $V_{\text{SYS}}$ ) continues dropping. If  $V_{\text{SYS}}$  falls below  $V_{\text{BATT}}$ , the MP2672A enters battery supplement mode. The battery starts to supplement the system load along with the boost converter. In supplement mode, the battery FET operates as a virtual diode.

When V<sub>SYS</sub> falls 30mV below V<sub>BATT</sub>, the battery FET turns on, and its source-to-drain voltage is regulated at 24mV. As the battery discharge current rises, the virtual diode loop is saturated and the battery FET fully turns on. The source-to-drain voltage is the discharge current times the on resistance of the battery FET.

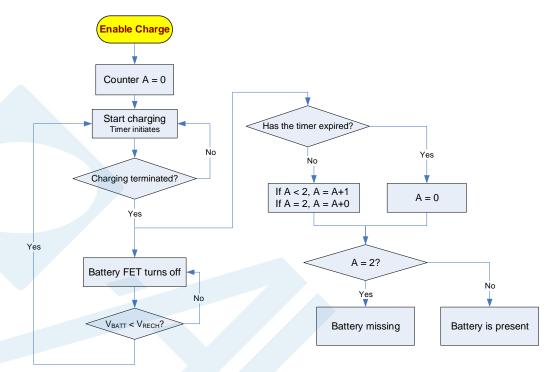

#### **Missing Battery Detection**

The MP2672A is capable of detecting whether a battery is connected. The device detects a missing battery under the following conditions:

- Charging is enabled

- Auto-recharge is triggered

- Recovery from any fault

If a battery cannot be found, a 1Hz blinking on the STAT pin indicates the missing battery condition, or the BATTFLOAT\_STAT bit is set 1 in host-control mode. Figure 10 shows the battery missing detection flowchart.

Figure 10: Missing Battery Detection Flowchart

#### **Battery Over-Voltage Protection**

The MP2672A is designed with a built-in battery over-voltage protection (OVP) threshold, which is 104% of  $V_{BATT\_REG}$ . If a battery OV event occurs, the MP2672A turns off the battery FET (Q3) and stops charging. At this time, the boost converter continues operating, and the system voltage tracks the battery voltage with additional  $V_{TRACK}$ .

When the balance function is enabled (the MID pin is not pulled down to AGND), the MP2672A uses the MID pin to monitor each cell's voltage. Generally, if any one of the cell's voltages exceeds 102.5% of  $V_{BATT\_REG}$  / 2, the MP2672A stops charging the battery.

#### **Safety Timer**

The MP2672A provides both a pre-charge and fast charge cycle safety timer to avoid an extended charging cycle due to abnormal battery conditions. When the battery is below V<sub>BATT\_PRE</sub>, the safety timer for pre-charge is 60 minutes. The fast charge cycle safety timer starts when the battery enters fast charge mode. The fast charge safety timer can be configured or disabled via the I<sup>2</sup>C.

The safety timer is reset at the beginning of a new charging cycle. It can also be reset by writing 0 and 1 sequentially to the REG00H, bit[4]. The following actions restart the safety timer:

- Beginning a new charge cycle

- Writing REG00H, bit[4] from 0 to 1 (charge enabled)

- Writing REG02H, bits[2:1] from 00 to 01/10/11 (safety timer enabled)

- Writing REG02H bit[3] from 0 to 1 (software reset)

In the event of an NTC hot or cold fault, the charging timer is suspended. Once the NTC fault is removed, the timer continues to count from the value it was at before the NTC fault.

#### **Watchdog Timer**

When the MP2672A operates in host-control mode, a watchdog timer is provided to reset all the registers to their default values if the watchdog timer is not reset periodically. By doing this, the MP2672A's register values return to their default settings when no action occurs on the I<sup>2</sup>C bus for a certain time. The watchdog timer duration can be configured and disabled via the I<sup>2</sup>C.

# Negative Temperature Coefficient (NTC) Thermistor

The term thermistor refers to any thermally sensitive resistor, and a negative temperature coefficient (NTC) thermistor is generally called a thermistor. Thermistors can be used for multiple purposes, as their characteristics are different based on their manufacturing method, structure, and shape. Unless otherwise noted, the thermistor resistance values are classified at a standard temperature of 25°C. The resistance of a thermistor is solely a function of its absolute temperature.

Refer to the thermistor's datasheet for the mathematic equation that calculates the relationship between resistance and the absolute temperature of the thermistor. It can also be calculated with Equation (3):

$$R_1 = R_2 \times e^{\beta \times \left(\frac{1}{T_1} - \frac{1}{T_2}\right)}$$

(3)

Where R1 is the resistance at the absolute temperature T1, R2 is the resistance at the absolute temperature T2, and  $\beta$  is a constant that depends on the thermistor's material.

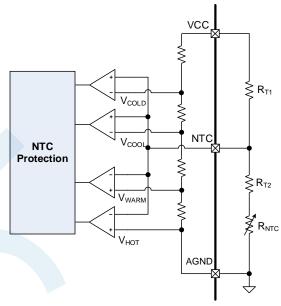

The MP2672A continuously monitors the battery's temperature by measuring the voltage on the NTC pins. This voltage is determined by the voltage divider. The voltage divider ratio is determined by the NTC thermistor's resistance values under different ambient battery temperatures.

The MP2672A internally sets a predetermined upper and lower bounds of the temperature range. If the voltage at the NTC pin goes out of the hot or cold threshold, the temperature is outside its safe operating limit. At this time, charging ceases until the operating temperature returns to within its safe range.

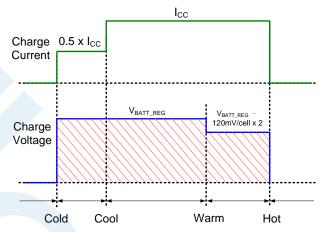

To satisfy JEITA requirements, the MP2672A monitors four temperature thresholds: the cold battery threshold ( $T_{NTC} < 0^{\circ}C$ ), the cool battery threshold ( $0^{\circ}C < T_{NTC} < 10^{\circ}C$ ), the warm battery threshold ( $45^{\circ}C < T_{NTC} < 60^{\circ}C$ ), and the hot battery threshold ( $T_{NTC} > 60^{\circ}C$ ).

For a given NTC thermistor, these temperatures correspond to the  $V_{\text{COLD}}$ ,  $V_{\text{COOL}}$ ,  $V_{\text{WARM}}$ , and  $V_{\text{HOT}}$  values. Figure 11 shows the typical JEITA operation when the battery temperature is in a

different temperature window, described in detail below:

- 1. When  $V_{NTC} < V_{HOT}$  or  $V_{NTC} > V_{COLD}$ , charging is suspended, and all timers are suspended.

- 2. When  $V_{HOT} < V_{NTC} < V_{WARM}$ , the battery regulation voltage ( $V_{BATT\_REG}$ ) is reduced by 120mV/cell from the configurable threshold.

- 3. When  $V_{COOL} < V_{NTC} < V_{COLD}$ , the charging current is reduced to half of the configurable charge current.

Figure 11: JEITA Compatible NTC Window

For a given thermistor, two of four temperature thresholds can be configured by changing the values of  $R_{T1}$  and  $R_{T2}$ . See the Selecting an NTC Sensor Resistor section on page 34 for more details.

#### Thermal Regulation and Thermal Shutdown

To guarantee safe operation, the MP2672A limits the die temperature. If the internal junction temperature reaches the preset threshold, the MP2672A starts to reduce the charge current to prevent greater power dissipation.

When  $V_{BATT} > V_{BATT\_PRE}$ , the die temperature limit is always set to 120°C. When  $V_{BATT} < V_{BATT\_PRE}$ , the die temperature limit can be configured to multiple values (60°C, 80°C, 100°C, or 120°C), which can be configured by the one-time programmable (OTP) register (REG05H, bits[4:3]).

If the junction temperature reaches 150°C, the boost converter enters shutdown mode.

#### Indications

The MP2672A has two open-drain pins (ACOK and STAT) to indicate the input power and charging status. Table 4 shows the behavior for each of these indications.

**Table 4: Input Power and Charging Statuses**

| Charging State                                                                                                         | ACOK | STAT            |

|------------------------------------------------------------------------------------------------------------------------|------|-----------------|

| Charging                                                                                                               | Low  | Low             |

| Charging complete, charging disabled                                                                                   | Low  | Open drain      |

| Charging suspended due to one of the following:  Battery OVP Timer fault NTC hot fault NTC cold fault Battery floating | Low  | 1Hz<br>blinking |

| Thermal shutdown                                                                                                       | Low  | Open drain      |

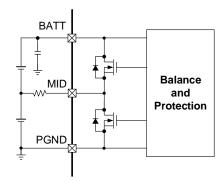

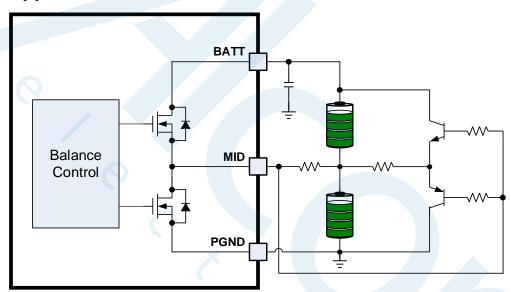

#### **Battery Cell Balance and Protection**

The MP2672A provides battery cell balance and protection for dual-cell applications (see Figure 12). The part can sense the voltage across each cell. Generally, if these two cells have voltages that are mismatched by more than 50mV, the internal discharge path turns on to discharge the cell with the higher voltage until the two cell voltages have a difference that is below 30mV.

If battery over-voltage protection (OVP) occurs before the two cells are equalized, charging is suspended.

The MP2672A integrates the balance path and control circuit. An external power dissipation resistor is also required to limit the balance current. If the cell balance function is not used, connect MID directly to AGND.

Figure 12: Battery Balance Block Diagram

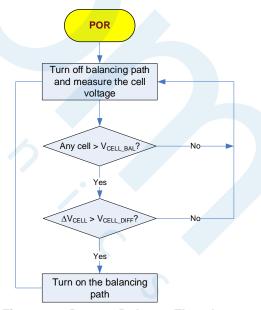

#### **Balancing Algorithm**

The balance block only operates in charge mode. Balancing starts when any cell voltage exceeds the balance start point (V<sub>CELL BAL</sub>).

The voltage difference between cells should exceed  $V_{\text{CELL\_DIFF}}$ . The MP2672A detects the cell voltages in the pack, then checks the voltage difference between two cells. If the differential voltage exceeds  $V_{\text{CELL\_DIFF}}$ , the corresponding balance MOSFET turns on.

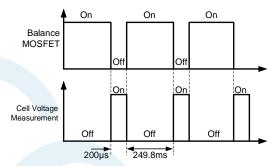

To measure the open-circuit voltage of the cell, balancing is frequently suspended for a short duration. Charging always operates independently of the balance algorithm if no other charging fault occurs. The cell voltage is measured for 200µs when cell balancing is suspended. Then cell balancing operates for 249.8ms each 250ms cycle (see Figure 13).

Figure 13: Battery Balance Clock

Figure 14 shows the battery balance flowchart.

Figure 14: Battery Balance Flowchart

For extremely unbalanced dual-cell batteries, the charger takes a few cycles to balance the battery voltages. For some applications, such as removable dual-cell batteries, a charger is required to balance two cells in one charge cycle. In this case, an external cell-balance circuit is recommended (see Figure 15).

The MP2672A also has an option to automatically disable termination if cell balancing is active. By doing this, the two cells are better matched once charging is terminated.

The cell voltage measured within the 200µs time is also delivered to the battery cell OVP block. If OVP occurs, charging is suspended (the battery FET turns off) until the measured cell voltage drops below the recovery threshold, which is set by REG00H, bit[0].

#### **Boost Converter Suspend Mode**

The MP2672A offers suspend mode to turn off the boost converter even when the input is present. In this mode, the SYS pin is powered by the battery through the internal battery FET, and the input quiescent current is optimized.

The MP2672A enters this mode by setting REG02H, bit[0] to 0. The MP2672A-000E is preset to this mode. The boost is suspended if any of the following conditions occur:

- Charging terminated

- Charging disabled

- An NTC fault has occurred

- A timer fault has occurred

- Battery over-voltage protection (OVP) has occurred

Figure 15: External Cell-Balancing Circuit

#### Series Interface

The IC uses two wires: a serial data (SDA) wire and serial clock (SCL) wire. All I<sup>2</sup>C master and slave devices are connected with these two wires. The master (e.g. a microcontroller or digital signal processor) generates the bus clock and initiates communication on the bus. The slave devices receive and respond to the bus commands from the master device. To communicate with a specific device, each slave device must have a unique bus address.

The I<sup>2</sup>C interface supports both standard mode (up to 100kbits), and fast mode (up to 400kbits). The SDA and SCL pins are open drains. Both the

SDA and SCL are connected to the positive supply voltage via a current source or pull-up resistor. When the bus is free, both lines are pulled high.

The MP2672A's SDA is a bidirectional line, and SCL is a unidirectional line.

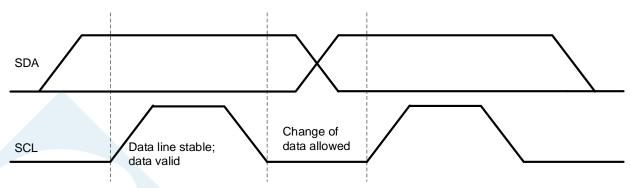

The data on the SDA line must be stable during the high period of the clock (see Figure 16). The high or low state of the data line can only change when the clock signal on the SCL line is low. One clock pulse is generated for each data bit transferred.

Figure 16: Bit Transfer on the I<sup>2</sup>C Bus

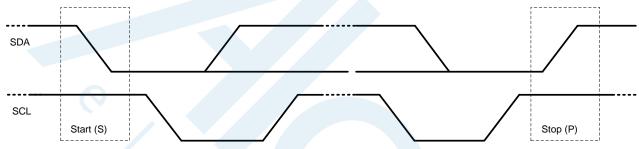

All transactions begin with a start (S) command and can be terminated by a stop (P) command. A start condition is defined as a high-to-low transition on the SDA line while SCL is high. A stop condition is defined as a low-to-high

transition on the SDA line when the SCL is high (see Figure 17). Start and stop conditions are always generated by the master. The bus is considered busy after a start condition, and free after a stop condition.

Figure 17: Start and Stop Conditions

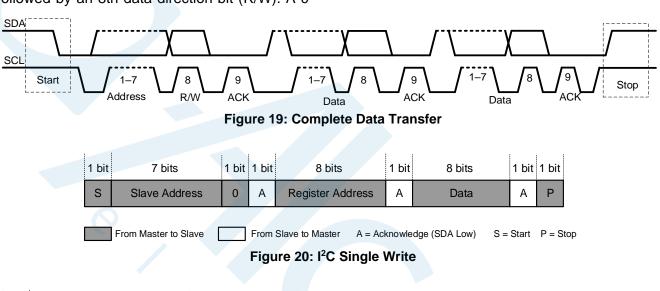

Data on the I<sup>2</sup>C bus is transferred in 8-bit packets (bytes) (see Figure 18). Each byte must be followed by an acknowledge bit (ACK). Data is transferred with the most significant bit (MSB) first.

An acknowledgement occurs after every byte. The acknowledge bit allows the receiver to signal to the transmitter that the byte was successfully received and another byte may be sent. All clock pulses, including the 9th acknowledge clock pulse, are generated by the master.

Figure 18: Data Transfer on the I<sup>2</sup>C Bus

The transmitter releases the SDA line during the acknowledge clock pulse so the receiver can pull the SDA line low. If it remains high during the 9th clock pulse, this is called a not acknowledge (NACK) signal. The master can then generate either a stop condition to abort the transfer, or a repeated start (S) to start a new transfer.

After the start condition is received, a slave address is sent. This address is 7 bits long followed by an 8th data direction bit (R/W). A 0

indicates a transmission (write) and a 1 indicates a request for data (read). Figure 19 shows the complete data transfer.

If the register address is not defined, the charger IC sends back a NACK signal and returns to the idle state.

The MP2672A operates as a slave device with the address 4BH. The MP2672A supports single-byte R/W (see Figure 20 and Figure 21).

| 1 bit | 7 bits        | 1 bit | 1 bit | 8 bits           | 1 bit | 1 bit | 7 bits        | 1 bit | 1 bit | 8 bits | 1 bit | 1 bit |

|-------|---------------|-------|-------|------------------|-------|-------|---------------|-------|-------|--------|-------|-------|

| S     | Slave Address | 0     | А     | Register Address | А     | S     | Slave Address | 1     | Α     | Data   | /A    | Р     |

From Master to Slave A = Acknowledge (SDA Low)

S = Start

From Slave to Master

/A = not Acknowledge (SDA High)

P = Stop

Figure 21: I<sup>2</sup>C Single Read

## I<sup>2</sup>C REGISTER MAP

#### **IC Address 4BH**

| Register Name | Address | R/W | Description                                                                         | Default   |

|---------------|---------|-----|-------------------------------------------------------------------------------------|-----------|

| REG00H        | 0x00    | R/W | Battery regulation voltage, charge configuration, and SYS voltage setting register. | 0011 1000 |

| REG01H        | 0x01    | R/W | Cell balance setting and charge current setting register.                           | 1000 1111 |

| REG02H        | 0x02    | R/W | Timer setting register.                                                             | 1001 0101 |

| REG03H        | 0x03    | R   | Status register.                                                                    | 0000 0000 |

| REG04H        | 0x04    | R   | Fault register.                                                                     | 0000 0000 |

## **REG 00H (Default: 0011 1000)**

| Bit | Name                      | POR | Reset by REG_RST | Reset<br>by WTD | R/W | Description                                      | Comment                                                                                          |

|-----|---------------------------|-----|------------------|-----------------|-----|--------------------------------------------------|--------------------------------------------------------------------------------------------------|

| 7   | V <sub>BATT_REG</sub> [2] | 0   | Y                | Y               | R/W | 000: 8.3V<br>001: 8.4V<br>010: 8.5V              | These bits set the battery                                                                       |

| 6   | V <sub>BATT_REG</sub> [1] | 0   | Y                | Y               | R/W | 010: 8.5V<br>011: 8.6V<br>100: 8.7V<br>101: 8.8V | regulation voltage. They are set to 001 by default. They are OTP-                                |

| 5   | VBATT_REG[0]              | 1   | Υ                | Υ               | R/W | 110: 8.9V<br>111: 8.2V                           | configurable.                                                                                    |

| 4   | CHG_CON<br>FIG            | 1   | Y                | Y               | R/W | 0: Charging disabled 1: Charging enabled         | This bit is set to 1 by default.                                                                 |

| 3   | VBATT_PRE[2]              | 1   | Y                | N               | R/W | 0.4V                                             | These bits set the system minimum voltage offset. It has a 6.0V offset, ranges                   |

| 2   | VBATT_PRE[1]              | 0   | Y                | N               | R/W | 0.2V                                             | between 6.0V and 6.7V,<br>and is set to 6.4V by<br>default.                                      |

| 1   | V <sub>BATT_PRE</sub> [0] | 0   | Υ                | N               | R/W | 0.1V                                             | This threshold is also used as the pre-charge battery voltage threshold. It is OTP-configurable. |

| 0   | CELL_OVP<br>HYS           | 0   | Y                | N               | R/W | 0: 80mV<br>1: 0mV                                | The bit sets the cell overvoltage protection (OVP) hysteresis.                                   |

**REG 01H (Default: 1000 1111)**

|     | Offi (Default, 1000 1111)     |     |                  |                 |     |                         |                                                                                                                   |

|-----|-------------------------------|-----|------------------|-----------------|-----|-------------------------|-------------------------------------------------------------------------------------------------------------------|

| Bit | Name                          | POR | Reset by REG_RST | Reset<br>by WTD | R/W | Description             | Comment                                                                                                           |

| 7   | NTC_TYPE                      | 1   | Y                | Y               | R/W | 0: Standard<br>1: JEITA | This bit is set to 0 by default. It is OTP-configurable.                                                          |

| 6   | Vcell_bal                     | 0   | Y                | Y               | R/W | 0: 3.5V<br>1: 3.7V      | This bit sets the cell-balance start point. It is set to 0 by default, and is OTP-configurable.                   |

| 5   | BALANCE_<br>THRESHOLD_<br>H2L | 0   | Y                | Y               | R/W | 0: 50mV<br>1: 70mV      | This bit sets the cell-balance threshold. It is set to 0 by default, and is OTP-configurable.                     |

| 4   | BALANCE_<br>THRESHOLD_<br>L2H | 0   | Y                | Y               | R/W | 0: 50mV<br>1: 70mV      | This bit sets the cell-balance threshold. It is set to 0 by default, and is OTP-configurable.                     |

| 3   | lcc[2]                        | 1   | Y                | Y               | R/W | 800mA                   | These bits set the fast charge current setting. If R <sub>ISET</sub> is 6kΩ:                                      |

| 2   | Icc[2]                        | Î   | Y                | Y               | R/W | 400mA                   | These bits have a 500mA offset, a 500mA to 2000mA range, and are set to 1111 by default.                          |

| 1   | lcc[1]                        | 1   | Y                | Y               | R/W | 200mA                   | If R <sub>ISET</sub> is 24kΩ:<br>These bits have a 125mA<br>offset, a 125mA to 500mA<br>range, are set to 1111 by |

| 0   | I <sub>CC</sub> [0]           | 1   | Υ                | Y               | R/W | 100mA                   | default, and are OTP-configurable.                                                                                |

**REG 02H (Default: 1001 0101)**

| Bit | Name                                    | POR | Reset by REG_RST | Reset<br>by WTD | R/W                         | Description                                                                               | Comment                                                                              |

|-----|-----------------------------------------|-----|------------------|-----------------|-----------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| 7   | f <sub>sw</sub>                         | 1   | Υ                | Y               | R/W 0: 600kHz<br>1: 1200kHz |                                                                                           | This bit is set to 1 by default. It is OTP-configurable.                             |

| 6   | I <sup>2</sup> C_WD_<br>TIMER_<br>RESET | 0   | Υ                | N               | R/W                         | 0: Normal<br>1: Reset                                                                     | This bit is set to 0 by default.                                                     |

| 5   | WD_TIMER<br>[1]                         | 0   | Y                | Ν               | R/W                         | 00: Disable timer<br>01: 40s                                                              | These bits set the I <sup>2</sup> C watchdog timer limit. They                       |

| 4   | WD_TIMER<br>[0]                         | 1   | Y                | N               | R/W                         | 10: 80s<br>11: 160s                                                                       | are set to 01 by default, and are OTP-configurable.                                  |

| 3   | REGISTER_<br>RESET                      | 0   | Y                | N               | R/W                         | 0: Keep current setting 1: Reset                                                          | This bit is set to 0 by default. After a reset, this bit returns to 0 automatically. |

| 2   | CHG_TMR[1]                              | 1   | Y                | Y               | R/W                         | 00: Disable charge timer 01: 8 hours                                                      | These bits are set to 10 by                                                          |

| 1   | CHG_TMR[0]                              | 0   | Y                | Y               | R/W                         | 10: 20 hours<br>11: 12 hours                                                              | default.                                                                             |

| 0   | EN_SUSP                                 | 1   | Y                | Y               | R/W                         | 0: Enable suspended mode (disable the boost) 1: Disable suspended mode (enable the boost) | This bit is set to 1 by default.                                                     |

**REG 03H (Default: 0000 0000)**

| Bit | Name               | POR | Reset by REG_RST | Reset<br>by WTD | R/W                                                                                                       | Description                                           | Comment                          |

|-----|--------------------|-----|------------------|-----------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------|

| 7   | RESERVED           | N/A | N/A              | N/A             | R                                                                                                         | Reserved.                                             | Reserved.                        |

| 6   | RESERVED           | N/A | N/A              | N/A             | R                                                                                                         | Reserved.                                             | Reserved.                        |

| 5   | CHG_STAT[1]        | 0   | N/A              | N/A             | R 00: Not charging 01: Pre-charge 10: Constant current or constant voltage charge R 11: Charging complete |                                                       | These bits are set to 00         |

| 4   | CHG_STAT[0]        | 0   | N/A              | N/A             |                                                                                                           |                                                       | by default.                      |

| 3   | PPM_STAT           | 0   | N/A              | N/A             | R                                                                                                         | 0: Not in PPM<br>1: in VIN PPM                        | This bit is set to 0 by default. |

| 2   | BATTFLOAT_<br>STAT | 0   | N/A              | N/A             | R                                                                                                         | 0: Battery present 1: Battery missing                 | This bit is set to 0 by default. |

| 1   | THERM_<br>STAT     | 0   | N/A              | N/A             | R                                                                                                         | 0: Normal<br>1: Thermal<br>regulation                 | This bit is set to 0 by default. |

| 0   | VSYS_STAT          | 0   | N/A              | N/A             | R                                                                                                         | 0: Not in Vsysmin regulation 1: In Vsysmin regulation | This bit is set to 0 by default. |

**REG 04H (Default: 0000 0000)**

|     |                   |     |                     | 1               | 1   | T                                                                                | 1                                     |

|-----|-------------------|-----|---------------------|-----------------|-----|----------------------------------------------------------------------------------|---------------------------------------|

| Bit | Name              | POR | Reset by<br>REG_RST | Reset<br>by WTD | R/W | Description                                                                      | Comment                               |

| 7   | WD_FAULT          | 0   | N/A                 | N/A R           |     | 0: Normal operation<br>1: The watchdog<br>timer has expired                      | This bit is set to 0 by default.      |

| 6   | INPUT_FAULT       | 0   | N/A                 | N/A R           |     | 0: Normal operation<br>1: Input OVP has<br>occurred                              | This bit is set to 0 by default.      |

| 5   | THERMSD_<br>FAULT | 0   | N/A                 | N/A             | R   | 0: Normal operation<br>1: Thermal<br>shutdown                                    | This bit is set to 0 by default.      |

| 4   | TIMER_FAULT       | 0   | N/A                 | N/A             | R   | 0: Normal operation 1: The safety timer has expired                              | This bit is set to 0 by default.      |

| 3   | BAT_FAULT         | 0   | N/A                 | N/A             | R   | 0: Normal operation<br>1: Battery OVP has<br>occurred                            | This bit is set to 0 by default.      |

| 2   | NTC_FAULT[2]      | 0   | N/A                 | N/A             | R   | 000: Normal operation 001: An NTC cold                                           |                                       |

| 1   | NTC_FAULT[1]      | 0   | N/A                 | N/A R           |     | fault has occurred<br>010: An NTC cool<br>fault has occurred<br>011: An NTC warm | These bits are set to 000 by default. |

| 0   | NTC_FAULT[0]      | 0   | N/A                 | N/A             | R   | fault has occurred<br>100: An NTC hot<br>fault has occurred                      |                                       |

REG 05H (Default: 1110 0000) (10)

|     | (                      |     |                  |                 |     |                                                                                                                      |                                  |  |

|-----|------------------------|-----|------------------|-----------------|-----|----------------------------------------------------------------------------------------------------------------------|----------------------------------|--|

| Bit | Name                   | POR | Reset by REG_RST | Reset<br>by WTD | R/W | Description                                                                                                          | Comment                          |  |

| 7   | RCHG                   | 1   | N/A              | N/A             | N/A | 0: No charging after input start-up when VBATT > VRECH 1: Automatic charging after input start-up when VBATT > VRECH | This bit is set to 1 by default. |  |

| 6   | RESERVED               | 1   | N/A              | N/A             | N/A | Reserved.                                                                                                            | Reserved.                        |  |

| 5   | BALANCE_<br>EOC_EN     | 1   | N/A              | N/A             | N/A | 0: Do not suspend termination when cell balancing is active 1: Suspend termination when cell balancing is active     | This bit is set to 1 by default. |  |

| 4   | T <sub>J_REG</sub> [1] | 0   | N/A              | N/A             | N/A | 00: 120°C<br>01: 100°C                                                                                               | This bit is set to 00 by         |  |

| 3   | T <sub>J_REG</sub> [0] | 0   | N/A              | N/A             | N/A | 10: 80°C<br>11: 60°C                                                                                                 | default.                         |  |

| 2   | RESERVED               | N/A | N/A              | N/A             | N/A | Reserved.                                                                                                            | Reserved.                        |  |

| 1   | RESERVED               | N/A | N/A              | N/A             | N/A | Reserved.                                                                                                            | Reserved.                        |  |

| 0   | RESERVED               | N/A | N/A              | N/A             | N/A | Reserved.                                                                                                            | Reserved.                        |  |

REG 06H (Default: 0000 0011) (10)

| Bit | Name             | POR | Reset by REG_RST | Reset<br>by WTD | R/W           | Description                                                                      | Comment                          |

|-----|------------------|-----|------------------|-----------------|---------------|----------------------------------------------------------------------------------|----------------------------------|

| 7   | RESERVED         | N/A | N/A              | N/A             | N/A           | Reserved.                                                                        | Reserved.                        |

| 6   | RESERVED         | N/A | N/A              | N/A             | N/A           | Reserved.                                                                        | Reserved.                        |

| 5   | RESERVED         | N/A | N/A              | N/A             | N/A Reserved. |                                                                                  | Reserved.                        |

| 4   | RESERVED         | N/A | N/A              | N/A             | N/A           | Reserved.                                                                        | Reserved.                        |

| 3   | RESERVED         | N/A | N/A              | N/A             | N/A Reserved. |                                                                                  | Reserved.                        |

| 2   | RESERVED         | N/A | N/A              | N/A             | N/A           | Reserved.                                                                        | Reserved.                        |

| 1   | RESERVED         | 1   | N/A              | N/A             | N/A           | Reserved.                                                                        | Reserved.                        |

| 0   | NVDC_MODE_<br>EN | 1   | N/A              | N/A             | N/A           | When charging is suspended: 0: Disable DC/DC switching 1: Enable DC/DC switching | This bit is set to 1 by default. |

#### Note:

<sup>10)</sup> This register is for OTP only. It is not accessible.

## **OTP MAP**

| #                   | Bit[7]                  | Bit[6]    | Bit[5]                                               | Bit[4]        | Bit[3]                               | Bit[2]       | Bit[1]                  | Bit[0]          |

|---------------------|-------------------------|-----------|------------------------------------------------------|---------------|--------------------------------------|--------------|-------------------------|-----------------|

| 00H                 | OH VBATT_REG: 8.2V-8.9V |           |                                                      | N/A           | V <sub>BATT_PRE</sub> : 6.0V to 6.7V |              |                         | N/A             |

| 01H                 | NTC Type                | VCELL_BAL | VCELL_DIFF_HL                                        | VCELL_DIFF_LH | lcc: 500n                            | nA to 2000mA | $R_{ISET} = 6k\Omega$ ) |                 |

| 02H                 | FSW                     | N/A       | WATC                                                 | HDOG          | N/A                                  | N/A          | N/A                     | N/A             |

| 05H <sup>(10)</sup> | RCHG                    | N/A       | BALANCE_ T <sub>J_REG</sub> : 60°C EOC_EN 100°C , or |               |                                      | N/A          | N/A                     | N/A             |