# MPM3695-100

16V, 100A, Scalable, DC/DC Power Module with PMBus

# **DESCRIPTION**

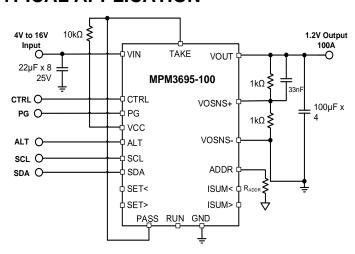

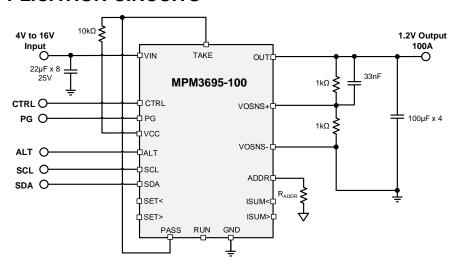

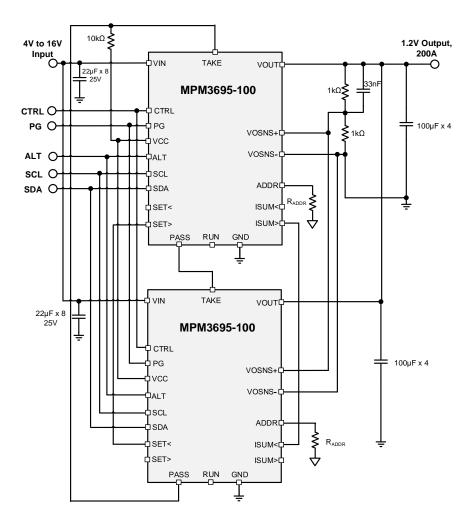

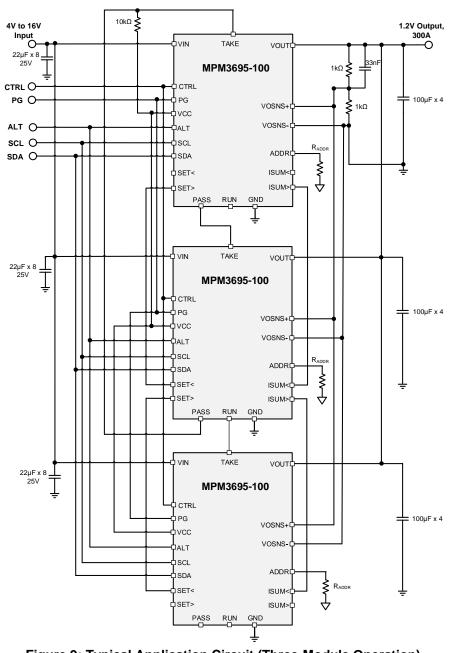

The MPM3695-100 is a 100A, scalable, fully integrated power module with a PMBus interface. The device offers a complete power solution that achieves up to 100A of output current, with excellent load and line regulation across a wide input voltage range. The MPM3695-100 operates at a high efficiency across a wide load range, and can be paralleled to deliver up to 800A of current.

By integrating four interleaved phases in a single molded power module, the MPM3695-100 adopts MPS's proprietary, multi-phase constant-on-time (MCOT) control to provide ultra-fast transient response and simple loop compensation. The PMBus interface provides module configurations and monitoring of key parameters.

Full protection features include over-current protection (OCP), over-voltage protection (OVP), under-voltage protection (UVP), and over-temperature protection (OTP).

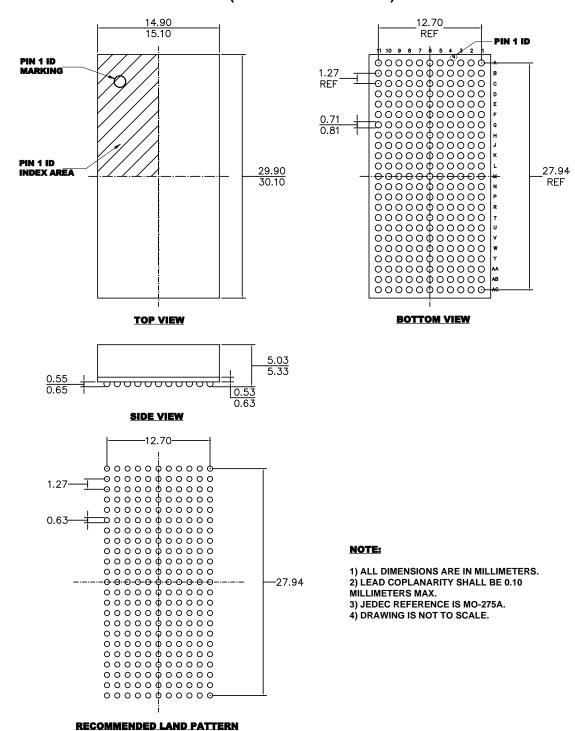

The MPM3695-100 requires a minimal number of readily available, external components. It is available in a BGA (15mmx30mmx5.18mm) package.

# **FEATURES**

- 3.2V to 16V Input Voltage Range with External 3.3V VCC Bias

- 4V to 16V Input Voltage Range with Internal VCC Bias

- 0.5V to 3.3V Output Voltage Range

- 100A Continuous Current for Outputs Up to 1.8V

- 60A Continuous Current for 3.3V Output

- Parallelable Up to 800A with Active Curernt Balancing

- Auto-Interleaving for Parallel Operation

- Output Voltage Remote Sensing

- ±1% Reference Voltage Accuracy (-40°C to +125°C)

- PMBus 1.3 Compliant

- Telemetry Readback including V<sub>IN</sub>, V<sub>OUT</sub>, I<sub>OUT</sub>, Temperature, and Faults

- Configurable via the PMBus:

- Output Voltage

- Soft-Start Time

- Over-Current (OC), Over-Temperature (OT), Over-Voltage (OV), Under-Voltage (UV), Under-Voltage Lockout (UVLO) Limits

- o PWM Mode

- Switching Frequency

- Available in a BGA (15mmx30mmx5.18mm)

Package

## **APPLICATIONS**

- Telecom and Networking Systems

- Industrial Equipment

- Servers and Computing

- FPGA and ASIC Core Power

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

Singel 3 | B-2550 Kontich | Belgium | Tel. +32 (0)3 458 30 33 info@alcom.be | www.alcom.be Rivium 1e straat 52 | 2909 LE Capelle aan den IJssel | The Netherlands Tel. +31 (0)10 288 25 00 | info@alcom.nl | www.alcom.nl

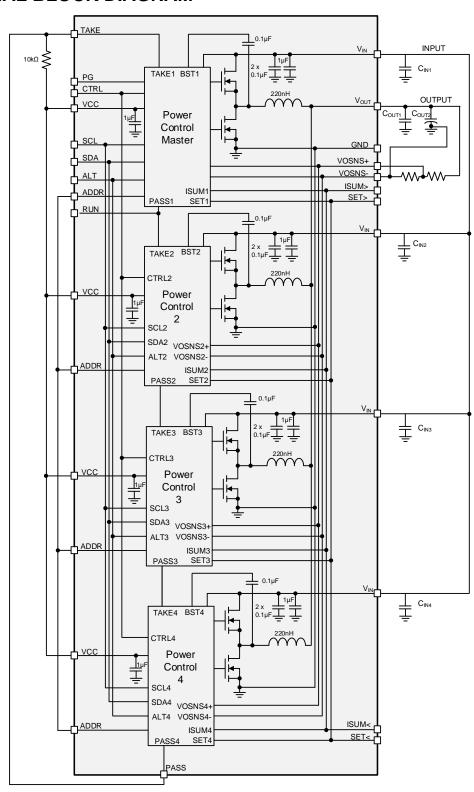

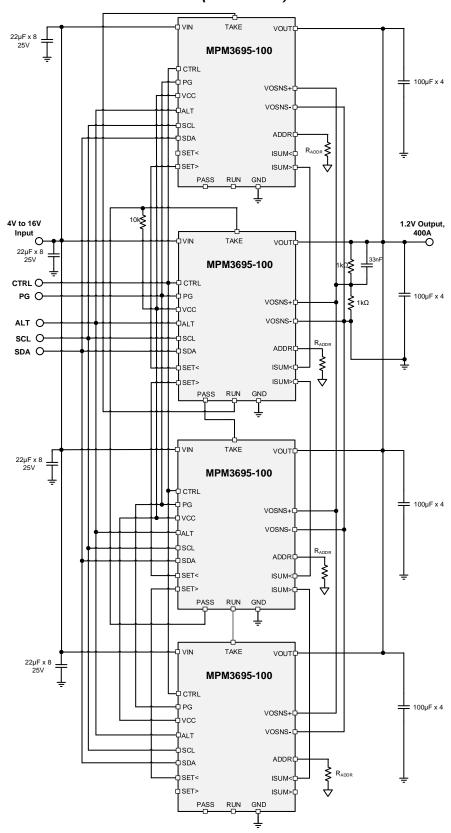

# **TYPICAL APPLICATION**

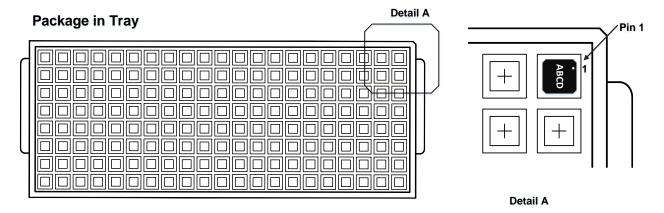

## ORDERING INFORMATION

| Part Number*          | Package                | Top Marking | MSL Rating |

|-----------------------|------------------------|-------------|------------|

| MPM3695GBH-100-xxxx** | BGA (15mmx30mmx5.18mm) | See Below   | 3          |

| MPM3695GBH-100-0001   | BGA (15mmx30mmx5.18mm) | See Below   | 3          |

| EVKT-MPM3695-100A     | -                      | -           | -          |

| EVKT-MPM3695-200A     | -                      | -           | -          |

| EVKT-MPM3695-400A     | -                      | -           | -          |

<sup>\*</sup> Add -T for tray package (e.g. MPM3695GBH-100-0001-T).

## **TOP MARKING**

MPS YYWW

M3695-100

LLLLLLLLL

M

MPS: MPS prefix YY: Year code WW: Week code

M3695-100: Part number LLLLLLLL: Lot number

M: Module

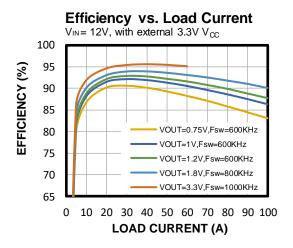

## MPM3695-100 EVALUATION KIT

Evaluation kit contents (items listed below can be ordered separately, and the GUI installation file and supplemental documents can be downloaded from the MPS website):

#### EVKT-MPM3695-100A: Single-Module Operation

| # | Part Number        | Item                                                                                | Qty |

|---|--------------------|-------------------------------------------------------------------------------------|-----|

| 1 | EVM3695-100-BH-00A | MPM3695GBH-100 evaluation board for single-module operation                         | 1   |

| 2 | EVKT-USBI2C-02     | USB to I <sup>2</sup> C communication interface device, USB cable, and ribbon cable | 1   |

## EVKT-MPM3695-200A: Dual-Module Operation

| # | Part Number        | Item                                                                                | Qty |

|---|--------------------|-------------------------------------------------------------------------------------|-----|

| 1 | EVM3695-100-BH-00B | MPM3695GBH-100 evaluation board for dual-module operation                           | 1   |

| 2 | EVKT-USBI2C-02     | USB to I <sup>2</sup> C communication interface device, USB cable, and ribbon cable | 1   |

<sup>\*\*</sup> The 4-digit suffix code "-xxxx" is the configuration identifier for the register settings stored in the non-volatile memory (NVM) of the power module. The default configuration code is "-0001". For customized configurations, contact an MPS FAE to assign a 4-digit suffix code.

# MPM3695-100 - 16V, 100A, SCALABLE DC/DC POWER MODULE WITH PMBUS

# EVKT-MPM3695-400A: Four-Module Operation

| # | Part Number        | Item                                                                                | Qty |

|---|--------------------|-------------------------------------------------------------------------------------|-----|

| 1 | EVM3695-100-BH-00C | MPM3695GBH-100 evaluation board for four-module operation                           | 1   |

| 2 | EVKT-USBI2C-02     | USB to I <sup>2</sup> C communication interface device, USB cable, and ribbon cable | 1   |

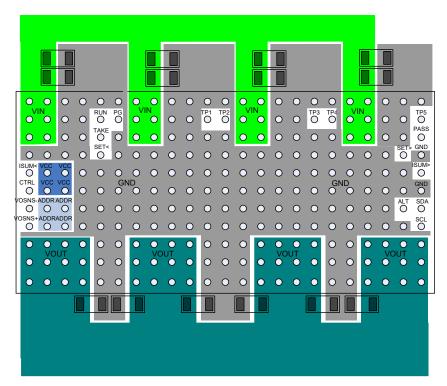

Figure 2: Evaluation Board Set-Up

4

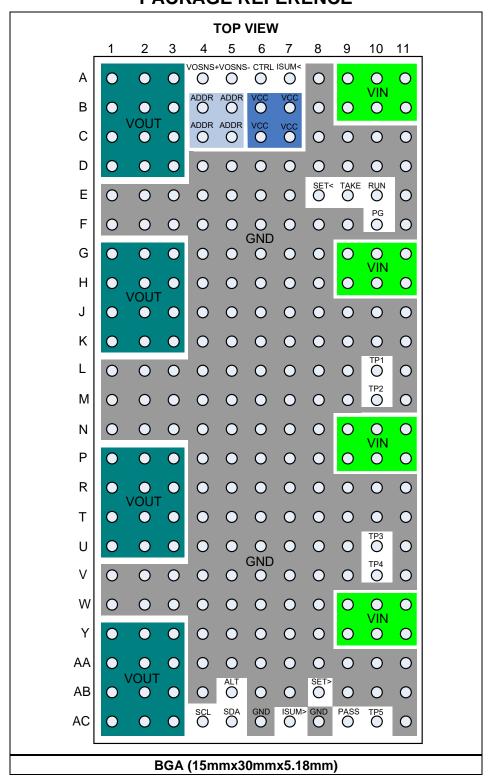

# **PACKAGE REFERENCE**

MPM3695-100 Rev. 1.0 MonolithicPower.com 5

3/25/2021 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

# **PIN NUMBER LIST**

Table 1: Pins A1~E11

| Pin | Name   | Pin | Name | Pin | Name | Pin | Name | Pin | Name |

|-----|--------|-----|------|-----|------|-----|------|-----|------|

| A1  | VOUT   | B1  | VOUT | C1  | VOUT | D1  | VOUT | E1  | GND  |

| A2  | VOUT   | B2  | VOUT | C2  | VOUT | D2  | VOUT | E2  | GND  |

| А3  | VOUT   | B3  | VOUT | C3  | VOUT | D3  | VOUT | E3  | GND  |

| A4  | VOSNS+ | B4  | ADDR | C4  | ADDR | D4  | GND  | E4  | GND  |

| A5  | VOSNS- | B5  | ADDR | C5  | ADDR | D5  | GND  | E5  | GND  |

| A6  | CTRL   | B6  | VCC  | C6  | VCC  | D6  | GND  | E6  | GND  |

| A7  | ISUM<  | B7  | VCC  | C7  | VCC  | D7  | GND  | E7  | GND  |

| A8  | GND    | B8  | GND  | C8  | GND  | D8  | GND  | E8  | SET< |

| A9  | VIN    | B9  | VIN  | C9  | GND  | D9  | GND  | E9  | TAKE |

| A10 | VIN    | B10 | VIN  | C10 | GND  | D10 | GND  | E10 | RUN  |

| A11 | VIN    | B11 | VIN  | C11 | GND  | D11 | GND  | E11 | GND  |

#### Table 2: Pins F1~K11

| Pin | Name |

|-----|------|-----|------|-----|------|-----|------|-----|------|

| F1  | GND  | G1  | VOUT | H1  | VOUT | J1  | VOUT | K1  | VOUT |

| F2  | GND  | G2  | VOUT | H2  | VOUT | J2  | VOUT | K2  | VOUT |

| F3  | GND  | G3  | VOUT | H3  | VOUT | J3  | VOUT | K3  | VOUT |

| F4  | GND  | G4  | GND  | H4  | GND  | J4  | GND  | K4  | GND  |

| F5  | GND  | G5  | GND  | H5  | GND  | J5  | GND  | K5  | GND  |

| F6  | GND  | G6  | GND  | H6  | GND  | J6  | GND  | K6  | GND  |

| F7  | GND  | G7  | GND  | H7  | GND  | J7  | GND  | K7  | GND  |

| F8  | GND  | G8  | GND  | H8  | GND  | J8  | GND  | K8  | GND  |

| F9  | GND  | G9  | VIN  | H9  | VIN  | J9  | GND  | K9  | GND  |

| F10 | PG   | G10 | VIN  | H10 | VIN  | J10 | GND  | K10 | GND  |

| F11 | GND  | G11 | VIN  | H11 | VIN  | J11 | GND  | K11 | GND  |

#### Table 3: Pins L1~R11

| Pin | Name |

|-----|------|-----|------|-----|------|-----|------|-----|------|

| L1  | GND  | M1  | GND  | N1  | GND  | P1  | VOUT | R1  | VOUT |

| L2  | GND  | M2  | GND  | N2  | GND  | P2  | VOUT | R2  | VOUT |

| L3  | GND  | M3  | GND  | N3  | GND  | P3  | VOUT | R3  | VOUT |

| L4  | GND  | M4  | GND  | N4  | GND  | P4  | GND  | R4  | GND  |

| L5  | GND  | M5  | GND  | N5  | GND  | P5  | GND  | R5  | GND  |

| L6  | GND  | M6  | GND  | N6  | GND  | P6  | GND  | R6  | GND  |

| L7  | GND  | M7  | GND  | N7  | GND  | P7  | GND  | R7  | GND  |

| L8  | GND  | M8  | GND  | N8  | GND  | P8  | GND  | R8  | GND  |

| L9  | GND  | M9  | GND  | N9  | VIN  | P9  | VIN  | R9  | GND  |

| L10 | TP1  | M10 | TP2  | N10 | VIN  | P10 | VIN  | R10 | GND  |

| L11 | GND  | M11 | GND  | N11 | VIN  | P11 | VIN  | R11 | GND  |

#### Table 4: Pins T1~Y11

| Pin | Name |

|-----|------|-----|------|-----|------|-----|------|-----|------|

| T1  | VOUT | U1  | VOUT | V1  | GND  | W1  | GND  | Y1  | VOUT |

| T2  | VOUT | U2  | VOUT | V2  | GND  | W2  | GND  | Y2  | VOUT |

| T3  | VOUT | U3  | VOUT | V3  | GND  | W3  | GND  | Y3  | VOUT |

| T4  | GND  | U4  | GND  | V4  | GND  | W4  | GND  | Y4  | GND  |

| T5  | GND  | U5  | GND  | V5  | GND  | W5  | GND  | Y5  | GND  |

| T6  | GND  | U6  | GND  | V6  | GND  | W6  | GND  | Y6  | GND  |

| T7  | GND  | U7  | GND  | V7  | GND  | W7  | GND  | Y7  | GND  |

| T8  | GND  | U8  | GND  | V8  | GND  | W8  | GND  | Y8  | GND  |

| Т9  | GND  | U9  | GND  | V9  | GND  | W9  | VIN  | Y9  | VIN  |

| T10 | GND  | U10 | TP3  | V10 | TP4  | W10 | VIN  | Y10 | VIN  |

| T11 | GND  | U11 | GND  | V11 | GND  | W11 | VIN  | Y11 | VIN  |

## Table 5: Pins AA1~AC11

| Pin  | Name | Pin  | Name | Pin  | Name  |

|------|------|------|------|------|-------|

| AA1  | VOUT | AB1  | VOUT | AC1  | VOUT  |

| AA2  | VOUT | AB2  | VOUT | AC2  | VOUT  |

| AA3  | VOUT | AB3  | VOUT | AC3  | VOUT  |

| AA4  | GND  | AB4  | GND  | AC4  | SCL   |

| AA5  | GND  | AB5  | ALT  | AC5  | SDA   |

| AA6  | GND  | AB6  | GND  | AC6  | GND   |

| AA7  | GND  | AB7  | GND  | AC7  | ISUM> |

| AA8  | GND  | AB8  | SET> | AC8  | GND   |

| AA9  | GND  | AB9  | GND  | AC9  | PASS  |

| AA10 | GND  | AB10 | GND  | AC10 | TP5   |

| AA11 | GND  | AB11 | GND  | AC11 | GND   |

# **PIN FUNCTIONS**

| Name            | Description                                                                                                                                                                                                                                                                                                      |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIN             | <b>Supply voltage.</b> This pin provides power to the module. Decoupling capacitors must be connected between VIN and GND.                                                                                                                                                                                       |

| VOUT            | Module output voltage node. Connect VOUT to a wide PCB copper plane.                                                                                                                                                                                                                                             |

| GND             | Power ground. Connect all GND pins together on a copper plane.                                                                                                                                                                                                                                                   |

| VCC             | <b>Output of the internal 3.3V LDO.</b> Connect all four VCC pins together for single-phase operation. For parallel operation, connect the VCC pins of the master phase and slave phases together.                                                                                                               |

| CTRL            | <b>Converter control.</b> CTRL is a digital input that turns the regulator on and off. Drive CTRL high to turn the regulator on; drive CTRL low to turn it off. Do not float this pin. For parallel operation, connect the CTRL pins of the master and slave phases together.                                    |

| VOSNS-          | <b>Output voltage sense negative return.</b> Connect this pin directly to the GND sense point of the load. Short VOSNS- to GND if remote sense is not used. For parallel operation, connect the VOSNS- pins of the master and slave phases together.                                                             |

| VOSNS+          | Output voltage sense positive return. Connect this pin to the output voltage $(V_{OUT})$ sense positive side to provide a feedback voltage $(V_{FB})$ to the system. For parallel operation, connect the VOSNS+ pins of the master and slave phases together.                                                    |

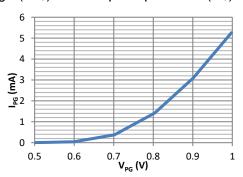

| PG              | <b>Multi-purpose power good output.</b> For the PG pin to pull high and indicate whether V <sub>OUT</sub> has exceeded 90% of the nominal voltage, a pull-up resistor must be connected to a DC voltage. There is a delay from PG going from low to high. Do not float this pin.                                 |

| PASS            | <b>Passes trigger signal to the TAKE pin.</b> Connect the PASS and TAKE pins for single-phase operation. For multi-phase operation, see the Typical Application Circuits section on page 47.                                                                                                                     |

| TAKE            | <b>Receives trigger signal from PASS pin or RUN signal.</b> Pull the TAKE pin of the master phase to 3.3V. Connect the PASS and TAKE pins for single-phase operation. For multi-phase operation, see the Typical Application Circuits section on page 47.                                                        |

| RUN             | <b>Trigger signal for slave phases.</b> Keep this pin floating for single-phase operation. For multi-phase operation, see the Typical Application Circuits section on page 47.                                                                                                                                   |

| SET<,<br>SET>   | <b>PWM signal setting.</b> The SET< and SET> pins are connected internally. Float the SET< and SET> pins for single-module operation. For multi-module operation, connect the SET pins of the master and slave phases together. Use either the SET< or SET> pin to connect to other MPM3695-100 devices          |

| ISUM<,<br>ISUM> | <b>Reference current output.</b> The ISUM< and ISUM> pins are connected internally. Float the ISUM< and ISUM> pins for single-module operation. For multi-module operation, connect the ISUM of the master and slave phases together. Use either the ISUM< or ISUM> pin to connect to other MPM3695-100 devices. |

| SCL             | PMBus serial clock.                                                                                                                                                                                                                                                                                              |

| SDA             | PMBus serial data.                                                                                                                                                                                                                                                                                               |

| ALT             | <b>PMBus alert.</b> Open-drain output, active low. A pull-up resistor must be connected from ALT to a 3.3V rail.                                                                                                                                                                                                 |

| ADDR            | <b>PMBus address setting pins.</b> Connect all four ADDR pins together. Connect a resistor from the ADDR pins to GND to set the device's address. For parallel operation, the same address should be selected for all modules.                                                                                   |

|                 | Test pins. Float these pins. Do not connect them.                                                                                                                                                                                                                                                                |

# **ABSOLUTE MAXIMUM RATINGS (1)** Supply voltage (V<sub>IN</sub>) ...... 18V V<sub>OUT</sub> ...... 5.5V V<sub>CC</sub> ...... 4.5V V<sub>CC</sub> (1s) (2) ...... 6V All other pins .....-0.3V to +4.3V All other pins (1s) (2) ...... 6V Continuous power dissipation (T<sub>A</sub> = 25°C) (3) ......24.95W Junction temperature ......170°C Storage temperature .....-65°C to +170°C ESD Ratings Human body model (HBM) .....±1000V Charged device model (CDM).....±750V Recommended Operating Conditions (4) Supply voltage (V<sub>IN</sub>) ......4V to 16V Output voltage (V<sub>OUT</sub>)..................0.5V to 3.3V External V<sub>CC</sub> bias ......3V to 3.6V Operating junction temp (T<sub>J</sub>).... -40°C to +125°C

####

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) Voltage rating during MTP programming.

- 3) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) T<sub>A</sub>) / θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation can produce an excessive die temperature.

- The device is not guaranteed to function outside of its operating conditions.

- 5) An external 3.3V  $V_{CC}$  bias is required. Writing to MTP memory is not supported with an external 3.3V  $V_{CC}$  bias.

- Measured on EVM3695-100-BH-00A, 25cmx15cm, 6-layer PCB.

- The value of θ<sub>JA</sub> given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 12V,  $T_J$  = -40°C to +125°C, unless otherwise noted.

| Parameters                                                     | Symbol                                | Condition                                                    | Min  | Тур   | Max  | Units            |

|----------------------------------------------------------------|---------------------------------------|--------------------------------------------------------------|------|-------|------|------------------|

| V <sub>IN</sub> Supply Current                                 |                                       |                                                              |      |       |      |                  |

| Shutdown supply current                                        | lin                                   | V <sub>CTRL</sub> = 0V                                       |      | 10    | 16   | mA               |

| Input Voltage                                                  |                                       |                                                              |      |       |      |                  |

| longit valtage renge                                           | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Internal VCC                                                 | 4    |       | 16   | V                |

| Input voltage range                                            | V <sub>IN</sub>                       | With external 3.3V Vcc                                       | 3.2  |       | 16   | V                |

| Output Voltage (8)                                             |                                       |                                                              |      | •     |      |                  |

| Output voltage range (8)                                       | Vout_range                            |                                                              | 0.5  |       | 3.3  | V                |

| Load regulation (8)                                            | Vout_dc_load                          | I <sub>OUT</sub> from 0A to 100A                             |      | ±0.5% |      | V <sub>OUT</sub> |

| Line regulation (8)                                            | Vout_dc_line                          | V <sub>IN</sub> from 4V to 16V,<br>I <sub>OUT</sub> = 100A   |      | ±0.5% |      | V <sub>оит</sub> |

| Current Limit                                                  |                                       |                                                              |      |       |      |                  |

| Individual valley current limit                                | I <sub>LIM</sub>                      | Individual phase current limit;<br>D7h, bits[4:0] = 5b'10010 |      | 27    |      | Α                |

| Minimum individual valley current limit configurable value (8) |                                       | Individual phase current limit                               |      | 1.5   |      | А                |

| Maximum individual valley current limit configurable value (8) |                                       | Individual phase current limit                               |      | 27    |      | А                |

| Individual low-side negative current limit in OVP              | ILIM_NEG_OVP                          | Individual phase current limit                               |      | -13   |      | Α                |

| CTRL                                                           |                                       |                                                              |      |       |      |                  |

| CTRL on threshold                                              | CTRLON                                |                                                              | 2.2  |       |      | V                |

| CTRL off threshold                                             | CTRLoff                               |                                                              |      |       | 1.2  | V                |

| Timing and Frequency                                           |                                       |                                                              |      |       |      |                  |

| Switching frequency (8)                                        | fsw                                   | Individual phase                                             |      | 600   |      | kHz              |

| Minimum on time (8)                                            | ton_min                               | $f_{SW} = 1000kHz, V_{OUT} = 0.6V$                           |      | 50    |      | ns               |

| Minimum off time (8)                                           | toff_min                              | V <sub>FB</sub> = 480mV                                      |      | 220   |      | ns               |

| Output Over-Voltage Protect                                    | tion (OVP) an                         | d Under-Voltage Protection (l                                | JVP) |       |      |                  |

| OVP threshold                                                  | Vovp                                  | D4h, bits[1:0] = 00                                          | 111% | 115%  | 119% | V <sub>REF</sub> |

| UVP threshold                                                  | V <sub>UVP</sub>                      | D9h, bits[3:2] = 10                                          | 75%  | 79%   | 83%  | $V_{REF}$        |

| Maximum configurable OVP threshold                             | V <sub>OVP_MAX</sub>                  | D4h, bits[1:0] = 11                                          | 126% | 130%  | 134% | $V_{REF}$        |

| Minimum configurable OVP threshold                             | V <sub>OVP_MIN</sub>                  | D4h, bits[1:0] = 00                                          | 111% | 115%  | 119% | V <sub>REF</sub> |

| Maximum configurable UVP threshold                             | Vuvp_max                              | D9h, bits[3:2] = 11                                          | 80%  | 84%   | 88%  | V <sub>REF</sub> |

| Minimum configurable UVP threshold                             | V <sub>UVP_MIN</sub>                  | D9h, bits[3:2] = 00                                          | 65%  | 69%   | 73%  | $V_{REF}$        |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN} = 12V$ ,  $T_J = -40$ °C to +125°C, unless otherwise noted.

| Parameters                                       | Symbol                     | Condition                                                                                        | Min  | Тур   | Max  | Units |

|--------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------|------|-------|------|-------|

| Analog-to-Digital Converter (                    | <b>ADC)</b> <sup>(8)</sup> |                                                                                                  |      |       |      |       |

| Voltage range                                    |                            |                                                                                                  | 0    |       | 1.28 | V     |

| ADC resolution                                   |                            |                                                                                                  |      | 10    |      | bits  |

| DNL                                              |                            |                                                                                                  |      | 1     |      | LSB   |

| Sample rate                                      |                            |                                                                                                  |      | 3     |      | kHz   |

| Digital-to-Analog Converter (                    | DAC) (Feedba               | ack Voltage)                                                                                     |      |       |      |       |

| Range (8)                                        |                            | 21h, bits[11:0] = 0x0258h;<br>29h, bits[9:0] = 0x01F4h                                           | 450  | 600   | 672  | mV    |

| Feedback accuracy                                | $V_{FB}$                   | 21h, bits[11:0] = 0x0258h;<br>29h, bits[9:0] = 0x01F4h                                           | 594  | 600   | 606  | mV    |

| Resolution                                       |                            | Per LSB                                                                                          |      | 2     |      | mV    |

| Feedback voltage with margin high <sup>(8)</sup> | V <sub>FB_MG_HIGH</sub>    |                                                                                                  |      | 672   |      | mV    |

| Feedback voltage with margin low (8)             | V <sub>FB_MG_LOW</sub>     |                                                                                                  |      | 450   |      | mV    |

| Soft Start and Turn-On/Off De                    | elay                       |                                                                                                  |      |       |      |       |

| Soft-start time (9)                              | t <sub>SS</sub>            | 61h, bits[2:0] = 3b'001                                                                          |      | 2     |      | ms    |

| Turn-on delay                                    | ton_delay                  | 60h, bits[7:0] = 0x00h                                                                           |      | 0     |      | ms    |

| Turn-off delay                                   | toff_delay                 | 64h, bits[7:0] = 0x00h                                                                           |      | 0     |      | ms    |

| Error Amplifier                                  |                            |                                                                                                  |      |       |      |       |

| Feedback current                                 | I <sub>FB</sub>            | V <sub>FB</sub> = V <sub>REF</sub> (V <sub>FB</sub> is the difference between VOSNS+ and VOSNS-) |      | 50    | 100  | nA    |

| Soft Shutdown                                    |                            |                                                                                                  |      |       |      |       |

| Soft shutdown discharge FET                      | Ron_disch                  | Individual phase                                                                                 |      | 60    |      | Ω     |

| Under-Voltage Lockout (UVL                       | O)                         |                                                                                                  |      |       |      |       |

| VCC UVLO rising threshold                        | VCC <sub>VTH</sub>         |                                                                                                  | 2.6  | 2.75  | 2.9  | V     |

| VCC UVLO threshold hysteresis                    | VCC <sub>HYS</sub>         |                                                                                                  |      | 250   |      | mV    |

| Minimum configurable input turn-on voltage       | V <sub>IN_ON_MIN</sub>     | V <sub>CC</sub> = 3.3V                                                                           | 2.65 | 2.9   | 3.1  | V     |

| Maximum configurable input turn-on voltage       | VIN_ON_MAX                 |                                                                                                  | 16   | 16.5  | 17   | V     |

| Minimum configurable input turn-off voltage      | VIN_OFF_MIN                | Vcc = 3.3V                                                                                       |      | 2.75  |      | V     |

| Maximum configurable input turn-off voltage (8)  | VIN_OFF_MAX                |                                                                                                  |      | 15.75 |      | V     |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN}$  = 12V,  $T_J$  = -40°C to +125°C, unless otherwise noted.

| Parameters                          | Symbol                   | Condition                                                                                  | Min   | Тур | Max   | Units     |

|-------------------------------------|--------------------------|--------------------------------------------------------------------------------------------|-------|-----|-------|-----------|

| Power Good (PG)                     |                          |                                                                                            |       |     |       |           |

| PG high threshold                   | PG <sub>VTH_HI</sub>     | V <sub>FB</sub> from low to high;<br>D9h, bits[1:0] = 01                                   |       |     |       | $V_{REF}$ |

| PG low threshold                    | PG <sub>VTH_LO</sub>     | V <sub>FB</sub> from high to low;<br>D9h, bits[3:2] = 10                                   |       | 79% |       | $V_{REF}$ |

| PG low-to-high delay                | tрдтр                    | D1h, bits[5:2] = 0000                                                                      |       | 2   |       | ms        |

| PG sink current capability          | $V_{PG}$                 | $I_{PG} = 10 \text{mA}$                                                                    |       |     | 0.3   | V         |

| PG leakage current                  | I <sub>PG_LEAK</sub>     | $V_{PG} = 3V$                                                                              |       | 1.5 |       | μA        |

| PC low lovel output voltage         | Vol_100                  | $V_{IN} = 0V$ , pull PGOOD up to 3.3V through a $100k\Omega$ resistor, $T_J = 25^{\circ}C$ |       | 600 | 720   | m۷        |

| PG low-level output voltage         | V <sub>OL_10</sub>       | $V_{IN} = 0V$ , pull PGOOD up to 3.3V through a $10k\Omega$ resistor, $T_J = 25^{\circ}C$  | 700   |     | 820   | IIIV      |

| Thermal Protection (TP)             |                          |                                                                                            |       |     |       |           |

| TP fault rising threshold (8)       | T <sub>SD_RISE</sub>     | 4Fh = 0x96h                                                                                |       | 150 |       | °C        |

| TP fault falling threshold (8)      | T <sub>SD_FALL</sub>     | 4Fh = 0x96h;<br>D6h, bits[2:1] = 01                                                        |       | 125 |       | °C        |

| TP warning rising threshold (8)     | Twarn_rise               | 51h = 0082h                                                                                |       | 130 |       | °C        |

| TP warning falling threshold (8)    | Twarn_fall               | 51h = 0082h;<br>D6h, bits[2:1] = 01                                                        |       | 105 |       | °C        |

| Min TP warning temperature (8)      | T <sub>SD_WARN_MIN</sub> |                                                                                            |       | 35  |       | °C        |

| Max TP warning temperature (8)      | T <sub>SD_WARN_MAX</sub> |                                                                                            |       | 160 |       | °C        |

| Monitoring Parameters               |                          |                                                                                            |       |     |       |           |

| Output voltage monitor accuracy (8) |                          | V <sub>OUT</sub> = 0.6V                                                                    | 0.588 | 0.6 | 0.612 | V         |

| Input voltage monitor accuracy      |                          |                                                                                            | 11.76 | 12  | 12.24 | V         |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN} = 12V$ ,  $T_J = -40$ °C to +125°C, unless otherwise noted.

| Parameters                              | Symbol                                               | Condition                           | Min  | Тур  | Max  | Units |  |  |  |  |

|-----------------------------------------|------------------------------------------------------|-------------------------------------|------|------|------|-------|--|--|--|--|

| PMBus DC Characteristics                | PMBus DC Characteristics (SDA, SCL, ALERT, CTRL) (8) |                                     |      |      |      |       |  |  |  |  |

| Input high voltage                      | V <sub>IH</sub>                                      |                                     |      |      | 2.1  | V     |  |  |  |  |

| Input low voltage                       | $V_{IL}$                                             |                                     | 0.8  |      |      | V     |  |  |  |  |

| Output low voltage                      | Vol                                                  | I <sub>OL</sub> = 1mA               |      |      | 0.4  | V     |  |  |  |  |

| Input leakage current                   | I <sub>LEAK</sub>                                    | SDA, SCL, ALERT = 3.3V              | -10  |      | +10  | μΑ    |  |  |  |  |

| Maximum voltage (SDA, SCL, ALERT, CTRL) | V <sub>MAX</sub>                                     | Transient voltage including ringing | -0.3 | 3.3  | +3.6 | V     |  |  |  |  |

| Pin capacitance on SDA, SCL             | CPIN                                                 |                                     |      |      | 10   | pF    |  |  |  |  |

| PMBus Timing Characteristics (8)        |                                                      |                                     |      |      |      |       |  |  |  |  |

| Min operating frequency                 |                                                      |                                     |      | 10   |      | kHz   |  |  |  |  |

| Max operating frequency                 |                                                      |                                     |      | 1000 |      | kHz   |  |  |  |  |

| Bus free time                           |                                                      | Between a stop and start condition  | 4.7  |      |      | μs    |  |  |  |  |

| Hold time                               |                                                      |                                     | 4.0  |      |      | μs    |  |  |  |  |

| Repeated start condition set-up time    |                                                      |                                     | 4.7  |      |      | μs    |  |  |  |  |

| Stop condition set-up time              |                                                      |                                     | 4.0  |      |      | μs    |  |  |  |  |

| Data hold time                          |                                                      |                                     | 300  |      |      | ns    |  |  |  |  |

| Data set-up time                        |                                                      |                                     | 250  |      |      | ns    |  |  |  |  |

| Clock low timeout                       |                                                      |                                     | 25   |      | 35   | ms    |  |  |  |  |

| Clock low period                        |                                                      |                                     | 4.7  |      |      | μs    |  |  |  |  |

| Clock high period                       |                                                      |                                     | 4.0  |      | 50   | μs    |  |  |  |  |

| Clock/data falling time                 |                                                      |                                     |      |      | 300  | ns    |  |  |  |  |

| Clock/data rising time                  |                                                      |                                     |      |      | 1000 | ns    |  |  |  |  |

#### Notes:

- 8) Guaranteed by sample characterization.

- 9) Guaranteed by sample characterization. Not tested in production. The parameter is tested during parameters characterization.

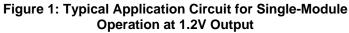

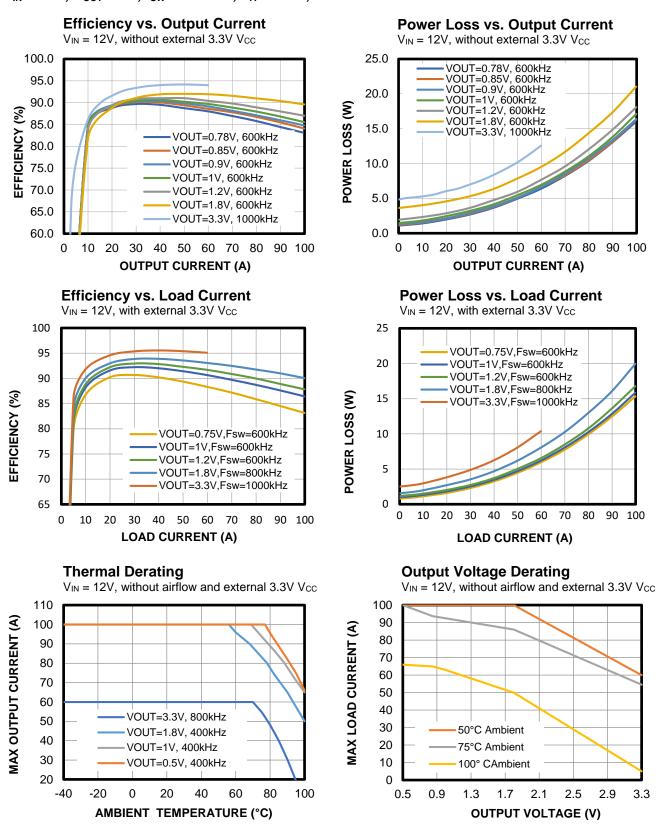

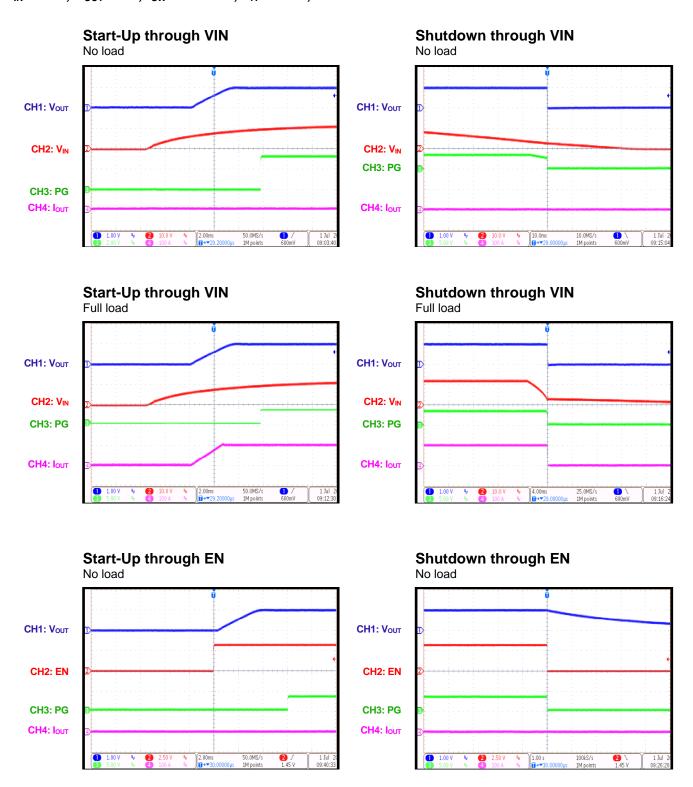

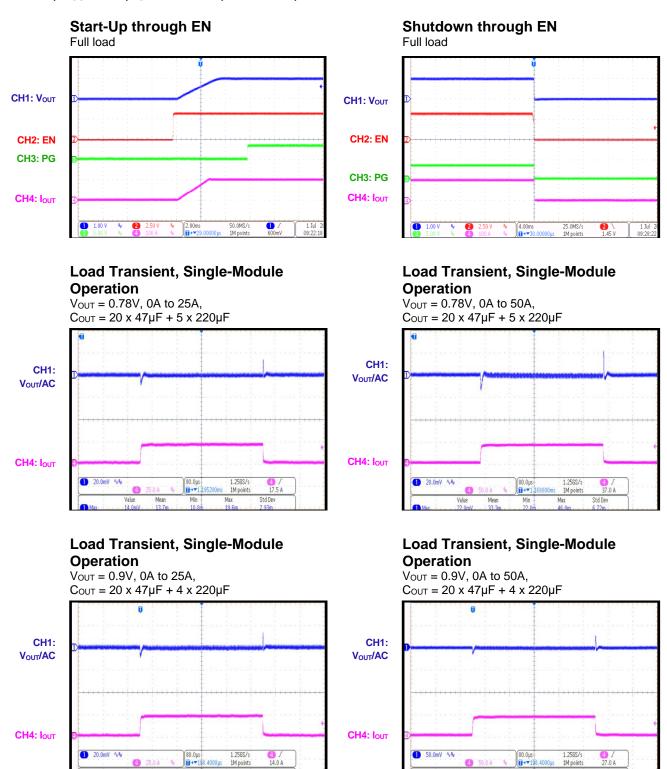

# TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN}$  = 12V,  $V_{OUT}$  = 1V,  $f_{SW}$  = 600kHz,  $T_A$  = 25°C, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN} = 12V$ ,  $V_{OUT} = 1V$ ,  $f_{SW} = 600$ kHz,  $T_A = 25$ °C, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN} = 12V$ ,  $V_{OUT} = 1V$ ,  $f_{SW} = 600$ kHz,  $T_A = 25$ °C, unless otherwise noted.

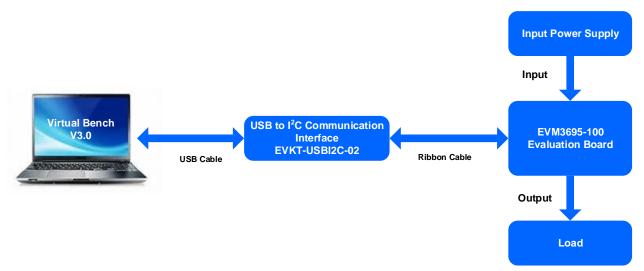

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 3: Functional Block Diagram

#### **OPERATION**

The MPM3695-100 is a fully integrated power module with up to 100A of continuous output current on a BGA (15mmx30mmx5.18mm) package. For applications that require more than 100A, up to eight MPM3695-100 modules can be connected in parallel to deliver an output current up to 800A. The MPM3695-100 employs multiphase constant-on-time (MCOT) control to provide fast transient response. Internal ramp compensation guarantees stable operation for applications using zero-ESR ceramic output capacitors.

# **Poly-Phase Architecture**

The MPM3695-100 integrates four sets of half-bridges with a power controller in each module. In single-module operation, the four phases are phase-shifted by 90° to minimize the output voltage ripple. One of the internal phases must be configured as the master phase, and the other three phases are slave phases.

## **MCOT Operation: Master Phase**

The master phase performs the following functions:

- Accepts both write and read commands through the PMBus from a host.

- Generates the SET signal.

- Manages start-up, shutdown, and all of the protection functions.

- Monitors fault alerts from the slave phases through the PG pin.

- Generates the first on pulse.

- Generates the on pulse when receiving RUN and SET signals.

- Dynamically adjusts its on time to ensure equal current sharing.

- Generates the PASS signal.

## **MCOT Operation: Slave Phases**

The slave phases perform the following functions:

- Accept write commands through the PMBus from a host.

- Receive SET signal(s) from a master phase.

- Start the on pulse when receiving RUN and SET signals.

- Dynamically adjust their on time to ensure equal current sharing on their own phase based on the per-phase and total current.

- Generate the PASS signal

#### **Parallel Operation**

In parallel configuration, one master module and up to seven slave modules are connected in parallel. The output current (IOUT) is shared equally between all MPM3695-100 power modules with active current balancing. The Typical Application Circuits section on page 47 illustrates two and four MPM3695-100s in parallel configuration. In parallel operation, each switching period is divided by up to eight interleaved phases with 45° phase-shifting. For four-module operation, two half-bridges are turned on simultaneously at each PWM pulse. The TAKE pin of the master module must be pulled up to a voltage source through a resistor. The MPM3695-100 detects its master/slave configuration by monitoring the state of the TAKE pin during start-up. The RUN and TAKE pins of all phases are connected in a cascaded manner.

#### Ramp Compensation

The MPM3695-100 operates with zero-ESR ceramic output capacitors by using internal ramp compensation. A triangular RAMP signal is generated internally, then superimposed onto the FB signal.

The triangular RAMP signal starts to rise once  $(V_{FB} + RAMP)$  drops below the reference signal and a SET pulse is generated. The RAMP signal rise time is fixed. The amplitude of the ramp compensation is selectable through register D0h, bits[3:1] to support a wide range of operation configurations.

There is a tradeoff between stability and load transient response. A larger RAMP signal provides better stability but slower load transient response, and vice versa. Optimize ramp compensation selection based on the design criteria for each application (see Table 6 on page 19).

# MPM3695-100 – 16V, 100A, SCALABLE DC/DC POWER MODULE WITH PMBUS

# **Table 6: Recommended Ramp and Resistor Divider Values**

| V <sub>IN</sub> (V) | V <sub>OUT</sub> (V) | fsw (kHz) | R <sub>1</sub> (kΩ) | $R_2$ (k $\Omega$ ) | Ramp (mV) | C <sub>FF</sub> (nF) |

|---------------------|----------------------|-----------|---------------------|---------------------|-----------|----------------------|

| 12                  | 0.78                 | 600       | 1                   | 3.3                 | 41        | 33                   |

| 12                  | 0.9                  | 600       | 1                   | 2                   | 41        | 33                   |

| 12                  | 1.0                  | 600       | 1                   | 1.5                 | 41        | 33                   |

| 12                  | 1.2                  | 600       | 1                   | 1                   | 41        | 33                   |

| 12                  | 1.8                  | 600       | 2                   | 1                   | 41        | 33                   |

| 12                  | 3.3                  | 1000      | 4.53                | 1                   | 41        | 33                   |

## PMBUS INTERFACE

#### **PMBus Serial Interface Description**

The Power Management Bus (PMBus) is an open-standard, power management protocol that defines a means of communication with power conversion and other devices.

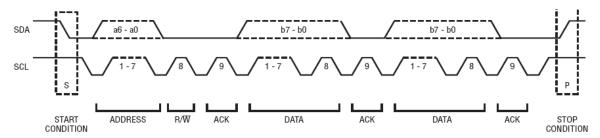

The PMBus is a two-wire, bidirectional, serial interface, consisting of a data line (SDA) and a clock line (SCL). The lines are externally pulled up to a bus voltage when they are in an idle state. When connecting to the lines, a master device generates the SCL signal and device address, then arranges the communication sequence. The MPM3695-100 is a PMBus slave device that supports both standard mode (100kHz) and fast modes (400kHz and 1000kHz).

#### Slave Address

A unique address should be set for each slave device that is connected to the same PMBus. The ADDR pin configures the address for the MPM3695-100. There is a 10µA current flowing out of the ADDR pin. Connect a resistor between the ADDR pin and AGND to set the ADDR voltage. The internal analog-to-digital converter (ADC) converts the ADDR pin voltage to set the PMBus address. A maximum of 16 addresses can be set by the ADDR pin. Table 7 lists the PMBus address for different resistor values. MFR\_ADDR\_PMBUS (D3h) can be used to digitally set the PMBus address.

For multi-phase configuration, the slave phases can share the same address as the master or they can have different addresses, depending on the application requirements. The slave phases can only accept write commands, which means they cannot accept read commands from the PMBus master. However, the master phase can accept both write and read commands from the PMBus master.

#### **Start and Stop Commands**

Start and stop commands are signaled by the master device to indicate the beginning and the end of the PMBus transfer. A start (S) command is defined as the SDA signal transitioning from high to low while SCL is high. A stop (P) command is defined as the SDA

signal transitioning from low to high while SCL is high (see Figure 4 on page 21).

Table 7: ADDR Resistor vs. PMBus Address

| $R_{ADDR}$ ( $k\Omega$ ) | Slave Address |

|--------------------------|---------------|

| 1.24                     | 30h           |

| 3.74                     | 31h           |

| 6.2                      | 32h           |

| 8.2                      | 33h           |

| 11.3                     | 34h           |

| 13.7                     | 35h           |

| 16.2                     | 36h           |

| 18.7                     | 37h           |

| 21                       | 38h           |

| 24                       | 39h           |

| 26.1                     | 3Ah           |

| 28.7                     | 3Bh           |

| 30.9                     | 3Ch           |

| 33                       | 3Dh           |

| 36                       | 3Eh           |

| 39                       | 3Fh           |

The master then generates the SCL clock signal(s) and transmits the device address and the read/write (R/W) direction bit on the SDA line. Data is transferred in 8-bit bytes by the SDA line. Each byte of data must be followed by an acknowledge (ACK) bit.

#### **PMBus Update Sequence**

The MPM3695-100 requires a start command, a valid PMBus address, a register address byte, and a data byte for a single data update. After receiving each byte, the MPM3695-100 acknowledges this process by pulling the SDA line low during the high period of a single clock pulse. A valid PMBus address selects the MPM3695-100. The MPM3695-100 performs an update on the falling edge of the LSB byte.

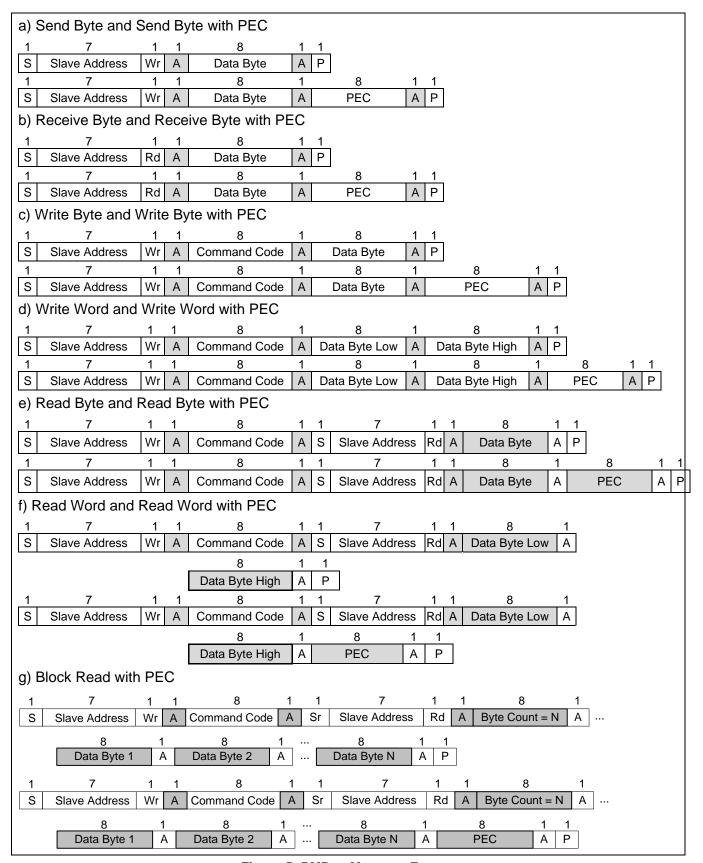

# **Protocol Usage**

All PMBus transactions on the MPM3695-100 are done using defined bus protocols. The following protocols can be implemented:

- Send byte with packet error checking (PEC)

- Receive byte with PEC

- Write byte with PEC

- Read byte with PEC

- Write word with PEC

- Read word with PEC

- Block read with PEC

#### **PMBus Message Format**

Figure 5 on page 22 shows the message formats. Unshaded cells indicate that the bus host is actively driving the bus; shaded cells indicate that the MPM3695-100 is driving the bus.

- S = Start condition

- Sr = Repeated start condition

- P = Stop condition

- R = Read bit

- W = Write bit

- A = Acknowledge bit (0)

- A = Acknowledge bit (1)

A represents the acknowledge (ACK) bit. The ACK bit is typically active low (logic 0) if the transmitted byte is successfully received by a device. However, when the receiving device is the bus master, the ACK bit for the last byte read is a logic 1, indicated by  $\overline{A}$ .

# Packet Error Checking (PEC)

The MPM3695-100's PMBus interface supports the use of the packet error checking (PEC) byte. The PEC byte is transmitted by the MPM3695-100 during a read transaction, or sent by the bus host to the MPM3695-100 during a write transaction.

The PEC byte detects errors during a bus transaction, depending on whether the transaction is a read or a write. If the host

determines that the PEC byte read during a read transaction is incorrect, it can decide to repeat the read if necessary. If the MPM3695-100 determines that the PEC byte sent during a write transaction is incorrect, it ignores the command (does not execute it) and sets a status flag. Within a group command, the host can choose to send or not send a PEC byte as part of the message to the MPM3695-100.

#### PMBus Alert Response Address (ARA)

The PMBus alert response address (ARA) is a special address that can be used by the bus host to locate any devices with which it can communicate. A host typically uses a hardware interrupt pin to monitor the PMBus ALERT pins from a number of devices. When the host interrupt occurs, the host issues a message on the bus using the PMBus receive byte, or on the received byte with PEC protocol.

The special address used by the host is 0x0C. Any devices that have a PMBus alert signal return their own 7-bit address as the 7MSB of the data byte. The LSB value is not used, and can be either 1 or 0. The host reads the device address from the received data byte and proceeds to handle the alert condition.

More than one device may have an active PMBus alert signal and attempt to communicate with the host. In this case, the device with the lowest address dominates the bus and succeeds in transmitting its address to the host. The device that succeeds disables its PMBus alert signal. If the host sees that the PMBus alert signal is still low, it continues to read addresses until all devices have successfully transmitted their addresses.

Figure 4: Data Transfer through the PMBus

Figure 5: PMBus Message Format

#### **Data and Numerical Formats**

The MPM3695-100 uses a direct internal format to represent real-world values such as voltage, current, power, and temperature.

All numbers with no suffix in this document are decimals, unless explicitly designated otherwise.

Numbers in binary format are indicated by the prefix "n'b", where n is the binary count. For example, 5'b01010 indicates a 5-bit binary data where the data is 01010.

The suffix "h" indicates a hexadecimal format, which is generally used for the register address number in this document.

The symbol "0x" indicates a hexadecimal format, which is used for the value in the register. For example, 0xA3 is a 1-byte number with a hexadecimal value of A3.

#### **PMBus Communication Failure**

A data transmission fault occurs when data is not properly transferred between the devices. There are several possible data transmission faults:

- Sending too little data

- Reading too little data

- Sending too many bytes

- Reading too many bytes

- Improperly set read bit in the address byte

- Unsupported command code

# **PMBus Reporting and Status Monitoring**

The MPM3695-100 supports real-time monitoring for some operation parameters and status with PMBus interface (see Table 8).

Table 8: PMBus Monitored Parameters and Statuses

| Parameter/Status                   | PMBus      |

|------------------------------------|------------|

| Output voltage (Vоит)              | 1.25mV/LSB |

| Output current (I <sub>OUT</sub> ) | 62.5mA/LSB |

| Temperature                        | 1°C/LSB    |

| Input voltage (V <sub>IN</sub> )   | 25mV/LSB   |

| V <sub>IN</sub> over-voltage (OV)  | ✓          |

| V <sub>IN</sub> under-voltage (UV) | ✓          |

| V <sub>IN</sub> OV warning         | ✓          |

| V <sub>IN</sub> UV warning         | ✓          |

| V <sub>OUT</sub> OV                | ✓          |

| V <sub>OUT</sub> UV                | ✓          |

| Over-temperature (OT)              | ✓          |

| OT warning                         | <b>√</b>   |

| V <sub>OUT</sub> over-current (OC) | ✓          |

| V <sub>OUT</sub> OC                | ✓          |

# **MTP Programming**

The MPM3695-100 has a built-in, multiple-time programmable (MTP) memory to store user configurations. The standard command register STORE\_USER\_ALL (15h) is not supported by the MPM3695-100. Instead, the MTP cells can be configured using the following command combination:

- 1. E7h (2000h)

- 2. E7h (1000h)

- 3. E7h (4000h)

In the GUI, the above commands are integrated together and named STORE\_USER\_ALL (15h). This means that MPS's GUI supports the 15h command.

When the MTP is being configured, the VCC voltage ( $V_{\text{CC}}$ ) may reach as high as 5V. Ensure that VCC is connected to circuits that can withstand this voltage. MTP configuration typically takes about 300ms.

# **REGISTER MAP**

| Name                       | Code | Туре               | Bytes | Default Value                      | MTP      |

|----------------------------|------|--------------------|-------|------------------------------------|----------|

| OPERATION                  | 01h  | R/W with PEC       | 1     | 0x80                               | ✓        |

| ON_OFF_CONFIG              | 02h  | R/W with PEC       | 1     | 0x1e                               | ✓        |

| CLEAR_FAULTS               | 03h  | Send byte with PEC | 0     | -                                  | •        |

| WRITE_PROTECT              | 10h  | R/W with PEC       | 1     | 0x00                               | <b>√</b> |

| STORE_USER_ALL             | 15h  | Send byte with PEC | 0     | -                                  | 1        |

| RESTORE_USER_ALL           | 16h  | Send byte with PEC | 0     | -                                  | -        |

| CAPABILITY                 | 19h  | R with PEC         | 1     | 0xB0                               | •        |

| VOUT_MODE                  | 20h  | R with PEC         | 1     | 0x40                               | -        |

| VOUT_COMMAND               | 21h  | R/W with PEC       | 2     | 0x0258 (1.2V)                      | ✓        |

| VOUT_MAX                   | 24h  | R/W with PEC       | 2     | 0x0BB8 (6V)                        | ✓        |

| VOUT_MARGIN_HIGH           | 25h  | R/W with PEC       | 2     | 0x02A0 (1.344V)                    | ✓        |

| VOUT_MARGIN_LOW            | 26h  | R/W with PEC       | 2     | 0x01FE (1.02V)                     | ✓        |

| VOUT_SCALE_LOOP            | 29h  | R/W with PEC       | 2     | 0x01F4 (0.5)                       | ✓        |

| VOUT_MIN                   | 2Bh  | R/W with PEC       | 2     | 0x00FA (0.5V)                      | ✓        |

| VIN_ON                     | 35h  | R/W with PEC       | 2     | 0x0010 (4V)                        | ✓        |

| VIN_OFF                    | 36h  | R/W with PEC       | 2     | 0x000B (2.75V)                     | ✓        |

| OT_FAULT_LIMIT             | 4Fh  | R/W with PEC       | 2     | 0x00A0(160°C)                      | <b>√</b> |

| OT_WARN_LIMIT              | 51h  | R/W with PEC       | 2     | 0x008C (140°C)                     | <b>√</b> |

| VIN_OV_FAULT_LIMIT         | 55h  | R/W with PEC       | 2     | 0x0024 (18V)                       | <b>√</b> |

| VIN_OV_WARN_LIMIT          | 57h  | R/W with PEC       | 2     | 0x0022 (17V)                       | <b>√</b> |

| VIN_UV_WARN_LIMIT          | 58h  | R/W with PEC       | 2     | 0x0001 (0.25V)                     | ✓        |

| TON_DELAY                  | 60h  | R/W with PEC       | 2     | 0x0000 (0ms)                       | ✓        |

| TON_RISE                   | 61h  | R/W with PEC       | 2     | 0x0002 (4ms)                       | ✓        |

| TOFF_DELAY                 | 64h  | R/W with PEC       | 2     | 0x0000 (0ms)                       | ✓        |

| STATUS_BYTE                | 78h  | R with PEC         | 1     | -                                  | -        |

| STATUS_WORD                | 79h  | R with PEC         | 2     | -                                  | -        |

| STATUS_VOUT                | 7Ah  | R with PEC         | 1     | -                                  | -        |

| STATUS_IOUT                | 7Bh  | R with PEC         | 1     | -                                  | -        |

| STATUS_INPUT               | 7Ch  | R with PEC         | 1     | -                                  | -        |

| STATUS_TEMPERATURE         | 7Dh  | R with PEC         | 1     | -                                  | -        |

| STATUS_CML                 | 7Eh  | R with PEC         | 1     | -                                  | -        |

| READ_VIN                   | 88h  | R with PEC         | 2     | -                                  | -        |

| READ_VOUT                  | 8Bh  | R with PEC         | 2     | -                                  | -        |

| READ_IOUT                  | 8Ch  | R with PEC         | 2     | -                                  | -        |

| READ_TEMPERATURE_1         | 8Dh  | R with PEC         | 2     | -                                  | _        |

| MFR CTRL COMP              | D0h  | R/W with PEC       | 1     | 0x0D                               | <b>√</b> |

| MFR_CTRL_VOUT              | D1h  | R/W with PEC       | 1     | 0x00                               | <b>√</b> |

| MFR CTRL OPS               | D2h  | R/W with PEC       | 1     | 0x03                               | ✓        |

| MFR ADDR PMBUS             | D3h  | R/W with PEC       | 1     | 0x30                               | <b>√</b> |

| MFR_VOUT_FAULT_LIMIT       | D4h  | R/W with PEC       | 1     | 0x03                               | <b>√</b> |

| MFR_OVP_NOCP_SET           | D5h  | R/W with PEC       | 1     | 0x02                               | ✓        |

| MFR_OT_OC_SET              | D6h  | R/W with PEC       | 1     | 0x09                               | ✓        |

| MFR_OC_PHASE_LIMIT         | D7h  | R/W with PEC       | 1     | 0x11 (102A total, 25.5A per phase) | ✓        |

| MFR_PGOOD_ON_OFF_<br>LIMIT | D9h  | R/W with PEC       | 1     | 0x00                               | <b>√</b> |

| MFR_VOUT_STEP              | DAh  | R/W with PEC       | 1     | 0x04                               | ✓        |

| MFR CTRL                   | EAh  | R/W with PEC       | 2     | 0xE8                               | ✓        |

|                            |      |                    |       | 1 5= 5                             |          |

## Note:

10) For manufacturer use. Write-only.

## **OPERATION (01h)**

The OPERATION command is a paged register. This command turns the converter output on and off in conjunction with input from the CTRL pin. It also sets V<sub>OUT</sub> to the upper or lower margin voltages. The device remains in the commanded operating mode until a subsequent OPERATION command (or a change in the state of the CTRL pin) instructs the converter to change to another mode.

This command can re-enable the converter after a fault-triggered shutdown. Writing an off command followed by an on command clears all faults. Writing only an on command after a fault-triggered shutdown does not clear the fault registers.

| Command       |     | OPERATION       |     |     |     |     |   |   |  |

|---------------|-----|-----------------|-----|-----|-----|-----|---|---|--|

| Format        |     | Unsigned binary |     |     |     |     |   |   |  |

| Bit           | 7   | 6               | 5   | 4   | 3   | 2   | 1 | 0 |  |

| Access        | R/W | R/W             | R/W | R/W | R/W | R/W | R | R |  |

| Function      |     |                 |     |     |     |     | ) | < |  |

| Default Value | 1   | 0               | 0   | 0   | 0   | 0   | 0 | 0 |  |

| Bits[7:6] | Bits[5:4] | Bits[3:2] | Bits[1:0] | On/Off        | Margin State               | 01h  |

|-----------|-----------|-----------|-----------|---------------|----------------------------|------|

| 00        | XX        | XX        | XX        | Immediate off | N/A                        | 0x00 |

| 01        | XX        | XX        | XX        | Soft shutdown | N/A                        | 0x60 |

| 10        | 00        | XX        | xx        | On            | Off                        | 0x80 |

| 10        | 01        | 01        | XX        | On            | Margin low (ignore fault)  | 0x94 |

| 10        | 01        | 10        | xx        | On            | Margin low (act on fault)  | 0x98 |

| 10        | 10        | 01        | xx        | On            | Margin high (ignore fault) | 0xA4 |

| 10        | 10        | 10        | XX        | On            | Margin high (act on fault) | 0xA8 |

#### ON\_OFF\_CONFIG (02h)

The ON\_OFF\_CONFIG command configures the combination of the CTRL pin input and PMBus commands required to turn the converter on and off. This includes how the converter responds when V<sub>IN</sub> is applied.

| Command       |   | ON_OFF_CONFIG   |   |     |     |      |          |       |  |

|---------------|---|-----------------|---|-----|-----|------|----------|-------|--|

| Format        |   | Unsigned binary |   |     |     |      |          |       |  |

| Bit           | 7 | 6               | 5 | 4   | 3   | 2    | 1        | 0     |  |

| Access        | R | R               | R | R/W | R/W | R/W  | R/W      | R     |  |

| Function      |   | Χ               |   | ON  | OP  | CTRL | POL_CTRL | DELAY |  |

| Default value | 0 | 0               | 0 | 1   | 1   | 1    | 1        | 0     |  |

#### ON

The ON bit sets the default to either operate whenever  $V_{IN}$  is present, or for the on/off operation to be controlled by the CTRL pin and PMBus commands.

| Bit[4] Value | Description                                                                                                          |

|--------------|----------------------------------------------------------------------------------------------------------------------|

| 0            | The converter starts up any time $V_{\text{IN}}$ is present, regardless of the state of the CTRL pin.                |

| 1            | The converter does not start up unless commanded by the CTRL pin and OPERATION command (as configured in bits[3:0]). |

#### OP

The OP bit controls how the converter responds to OPERATION commands.

| Bit[3] Value | Description                                                                   |

|--------------|-------------------------------------------------------------------------------|

| 0            | The converter ignores the ON bit in the OPERATION command from the PMBus.     |

| 1            | The converter responds to the ON bit in the OPERATION command from the PMBus. |

MPM3695-100 Rev. 1.0 MonolithicPower.com 25

#### **CTRL**

The CTRL bit controls how the converter responds to the CTRL pin.

| Bit[2] Value | Description                                                                                                                                                                 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0            | The converter ignores the CTRL pin (the device turning on and off is only controlled by the OPERATION command).                                                             |

| 1            | The converter requires the CTRL pin to be asserted to start up. Depending on bit[3] (OP), the OPERATION command may also be required to instruct the converter to start up. |

#### POL CTRL

The POL CTRL bit sets the polarity of the CTRL pin. This function is disabled.

| Bit[1] Value | Description                                                  |

|--------------|--------------------------------------------------------------|

| 0            | Active low (pull the CTRL pin low to start the converter).   |

| 1            | Active high (pull the CTRL pin high to start the converter). |

#### **DELAY**

The DELAY bit sets the shutdown action when the converter is commanded off through the PMBus. This bit is read-only and cannot be modified by the end user.

| Bit[0] Value | Description            |

|--------------|------------------------|

| 0            | TOFF_DELAY, TOFF_FALL. |

#### CLEAR\_FAULTS (03h)

The CLEAR\_FAULTS command resets all stored warning and fault flags. If a fault or warning condition still exists when the CLEAR\_FAULTS command is issued, the ALT# signal may not be cleared, or may be reasserted almost immediately. Issuing a CLEAR\_FAULTS command does not cause the converter to restart in the event of a fault shutdown. To restart the device, issue an OPERATION on command after the fault condition is cleared. This command uses the PMBus to send the byte protocol.

## **WRITE PROTECT (10h)**

The WRITE\_PROTECT command controls writing to the converter. The provides protection against accidental changes.

All supported commands (registers) may have their parameters read, regardless of the WRITE\_PROTECT settings.

|   |               | Bits | [7:0] | Valu | ıe |   |   | Description                                                                                                  |

|---|---------------|------|-------|------|----|---|---|--------------------------------------------------------------------------------------------------------------|

| 0 | 0             | 0    | 0     | 0    | 0  | 0 | 0 | Enables writes to all registers.                                                                             |

| 0 | 0 1 0 0 0 0   |      |       |      |    |   | 0 | Disables all writes except to the WRITE_PROTECT, OPERATION, PAGE, ON_OFF_CONFIG, and VOUT_COMMAND registers. |

| 0 | 1             | 0    | 0     | 0    | 0  | 0 | 0 | Disables all writes except to the WRITE_PROTECT, OPERATION, and PAGE registers.                              |

| 1 | 1 0 0 0 0 0 0 |      |       |      |    | 0 | 0 | Disables all writes except to the WRITE_PROTECT register.                                                    |

When 10h is set to a value other than 0x00 to configure the MTP, register 15h can only be set through MPS's GUI. The MTP's E7h command cannot be used. For more details, see the MTP Programming section on page 23.

The default value for this register is 0x00.

#### STORE\_USER\_ALL (15h)

The STORE\_USER\_ALL command writes the data from the registers to the internal MTP(s). This occurs when the MPM3695-100 receives a STORE\_USER\_ALL command from the PMBus interface. The MPM3695-100 does not support the 15h command via the MTP. However, the device can accept the 15h command from MPS's GUI. For more details, see the MTP Programming section on page 23.

The following registers can be stored using STORE\_USER\_ALL:

- OPERATION (01h)

- ON\_OFF\_CONFIG (02h)

- WRITE PROTECT (10h)

- VOUT COMMAND (21h)

- VOUT\_MAX (24h)

- VOUT\_MARGIN\_HIGH (25h)

- VOUT\_MARGIN\_LOW (26h)

- VOUT\_SCALE\_LOOP (29h)

- VOUT\_MIN (2Bh)

- VIN\_ON (35h)

- VIN OFF (36h)

- OT\_FAULT\_LIMIT (4Fh)

- OT\_WARN\_LIMIT (51h)

- VIN\_OV\_FAULT\_LIMIT (55h)

- VIN\_OV\_WARN\_LIMIT (57h)

- VIN\_UV\_WARN\_LIMIT (58h)

- TON\_DELAY (60h)

- TON\_RISE (61h)

- TOFF DELAY (64h)

- MFR\_CTRL\_COMP (D0h)

- MFR\_CTRL\_VOUT (D1h)

- MFR CTRL OPS (D2h)

- MFR ADDR PMBUS (D3h)

- MFR VOUT FAULT LIMIT (D4h)

- MFR OVP NOCP SET (D5h)

- MFR\_OT\_OC\_SET (D6h)

- MFR OC PHASE LIMIT (D7h)

- MFR\_PGOOD\_ON\_OFF\_LIMIT (D9h)

- MFR VOUT STEP (DAh)

- MFR\_CTRL (EAh)

#### RESTORE\_USER\_ALL (16h)

The RESTORE\_USER\_ALL command instructs the MPM3695-100 to copy the entire contents of the MTP to the matching locations in the registers. The values in the registers are overwritten by the values retrieved from the MTP. Any items in the MTP that do not have matching locations in the operating memory are ignored.

This command can be used while the MPM3695-100 is operating, but the device may be unresponsive.

This command is write-only.

## **CAPABILITY (19h)**

The CAPABILITY command returns information about the PMBus functions supported by the MPM3695-100. This command is read with the PMBus read byte protocol.

| Command       |                                                             |        |         | CAPAI   | BILITY   |  |  |  |  |  |  |  |

|---------------|-------------------------------------------------------------|--------|---------|---------|----------|--|--|--|--|--|--|--|

| Format        |                                                             |        |         | Unsigne | d binary |  |  |  |  |  |  |  |

| Bit           | 7                                                           | 1      | 0       |         |          |  |  |  |  |  |  |  |

| Access        | R R R R R                                                   |        |         |         |          |  |  |  |  |  |  |  |

| Function      | PEC                                                         | MAX_BU | S_SPEED | ALERT   | X        |  |  |  |  |  |  |  |

| Default Value | 1                                                           | 0      | 1       | 1       | 0 0 0 0  |  |  |  |  |  |  |  |

| Details       | PEC supported, max speed 1MHz, supports PMBus alert and ARA |        |         |         |          |  |  |  |  |  |  |  |

| Bits[6:5 | 5] Value | Meaning                                    |

|----------|----------|--------------------------------------------|

| 0        | 0        | The maximum supported bus speed is 100kHz. |

| 0        | 1        | The maximum supported bus speed is 1MHz.   |

| 1        | 0        | The maximum supported bus speed is 400kHz. |

| 1        | 1        | Reserved.                                  |

The default value for this register is 0xB0.

#### VOUT\_MODE (20h)

The VOUT\_MODE command reads and commands  $V_{\text{OUT}}$ . The 3MSB are used to determine the data format (only direct format is supported), and the remaining 5 bits represent the exponent used in the  $V_{\text{OUT}}$  read/write commands.

The default value for this register is 0x40.

## **VOUT\_COMMAND (21h)**

The VOUT\_COMMAND command sets  $V_{OUT}$ . To calculate the feedback reference voltage, multiply VOUT\_COMMAND by VOUT\_SCALE\_LOOP.

For more details, see the Setting the Output Voltage section on page 43.

| Command       |           |   |   |   |     |                                     | VC | UT_C | AMMC | ND |   |   |   |   |     |     |

|---------------|-----------|---|---|---|-----|-------------------------------------|----|------|------|----|---|---|---|---|-----|-----|

| Format        |           |   |   |   |     |                                     |    | Dir  | ect  |    |   |   |   |   |     |     |

| Bit           | 15        |   |   |   |     |                                     |    |      |      |    |   |   |   |   | 0   |     |

| Access        | R         | R | R | R | R/W | R/W R/W R/W R/W R/W R/W R/W R/W R/W |    |      |      |    |   |   |   |   | R/W | R/W |

| Function      | X 2mV/LSB |   |   |   |     |                                     |    |      |      |    |   |   |   |   |     |     |

| Default Value | 0         | 0 | 0 | 0 | 0   | 0                                   | 1  | 0    | 0    | 1  | 0 | 1 | 1 | 0 | 0   | 0   |

The value is unsigned and 1LSB = 2mV. The default value of 21h is 1.2V, meaning the default value of this register is 0x0258.

#### VOUT MAX (24h)

The VOUT\_MAX command sets an upper limit on  $V_{OUT}$ , regardless of any other commands or combinations. VOUT\_MAX provides a safeguard against the user accidentally setting  $V_{OUT}$  too high. It does not replace over-voltage protection (OVP).

| Command       |           |                                      |   |   |     |     |     | VOUT | _MAX |     |     |     |     |     |     |     |

|---------------|-----------|--------------------------------------|---|---|-----|-----|-----|------|------|-----|-----|-----|-----|-----|-----|-----|

| Format        |           |                                      |   |   |     |     |     | Dir  | ect  |     |     |     |     |     |     |     |

| Bit           | 15        | 5 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |   |   |     |     |     |      |      |     |     |     |     |     |     |     |

| Access        | R         | R                                    | R | R | R/W | R/W | R/W | R/W  | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Function      | X 2mV/LSB |                                      |   |   |     |     |     |      |      |     |     |     |     |     | •   |     |

| Default Value | 0         | 1                                    | 0 | 1 | 1   | 1   | 0   | 1    | 1    | 1   | 0   | 0   | 0   |     |     |     |

If an attempt is made to set V<sub>OUT</sub> to a level that exceeds VOUT\_MAX, the device takes the following actions:

- 1. The commanded V<sub>OUT</sub> is set to VOUT MAX.

- 2. The VOUT bit is set in STATUS\_WORD.

- 3. The VOUT\_MAX\_MIN warning bit is set in the STATUS\_VOUT register.

- 4. The device notifies the host.

The value is unsigned and 1LSB = 2mV. The maximum value of VOUT\_MAX is 6V, and the default value is 6V. The default value of this register is 0x0BB8h.

# **VOUT\_MARGIN\_HIGH (25h)**

| Command       |           |    |    |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | VOU | T_MAF | RGIN_H | HIGH |   |   |   |   |     |   |