# **Datasheet**

Lyra 24S

Version 1.0

# **REVISION HISTORY**

| Version | Date        | Notes           | Contributors                                      | Approver      |

|---------|-------------|-----------------|---------------------------------------------------|---------------|

| 1.0     | 24 May 2023 | Initial Release | Robert Gosewehr,<br>Raj Khatri,<br>Dave Drogowski | Jonathan Kaye |

|         |             |                 |                                                   |               |

## **CONTENTS**

| 1  | Introd | duction                                                                                     | 5  |

|----|--------|---------------------------------------------------------------------------------------------|----|

| 1. | .1     | Key Features                                                                                | 5  |

| 1. | .2     | Hardware Features                                                                           | 6  |

| 1. | .3     | Firmware Options                                                                            | 7  |

| 2  | Orde   | ring Information                                                                            | 7  |

| 3  | Syste  | em Overview                                                                                 | 8  |

| 3. | .1     | Block Diagram                                                                               | 8  |

| 3. | .2     | EFR32BG24 SoC                                                                               | 9  |

| 3. | .3     | Integrated Antenna                                                                          | 9  |

| 3. | .4     | External Antenna                                                                            | 9  |

| 3. | .5     | Power Supply                                                                                | 10 |

| 3. | .6     | General Purpose Input/Output (GPIO)                                                         | 10 |

| 3. | .7     | Security                                                                                    | 10 |

| 4  | Elect  | rical Specifications                                                                        | 13 |

| 4. | .1     | Absolute Maximum Ratings                                                                    | 13 |

| 4. | .2     | General Operating Conditions                                                                | 14 |

| 4. | .3     | MCU Current Consumption at 3.0V                                                             | 14 |

| 4. | .4     | Radio Current Consumption with 3.0 V Supply                                                 | 16 |

| 4. | .5     | RF Transmitter General Characteristics for the 2.4 GHz Band                                 |    |

| 4. | .6     | RF Receiver General Characteristics for the 2.4 GHz Band                                    | 17 |

| 4. | .7     | RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 1 Mbps Data Rate   | 17 |

| 4. | .8     | RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 2 Mbps Data Rate   | 18 |

| 4. | .9     | RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 500 kbps Data Rate | 19 |

| 4. | .10    | RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 125 kbps Data Rate | 20 |

| 4. | .11    | High-Frequency Crystal                                                                      | 21 |

| 4. | .12    | Low-Frequency Crystal Oscillator                                                            | 21 |

| 4. | .13    | Precision Low Frequency RC Oscillator (LFRCO)                                               | 22 |

| 4. | .14    | GPIO Pins                                                                                   | 22 |

| 4. | .15    | Microcontroller Peripherals                                                                 | 23 |

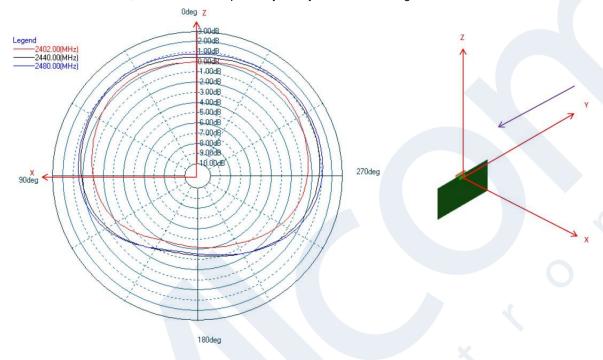

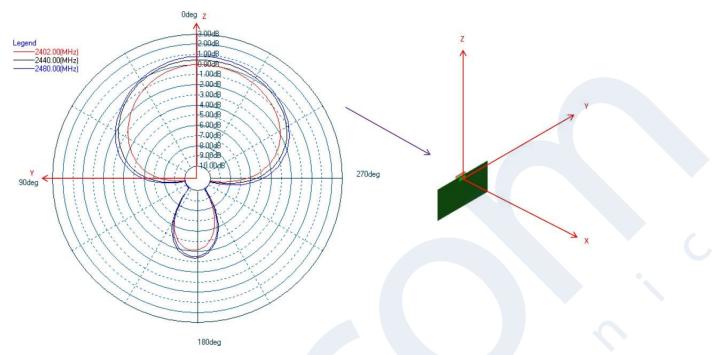

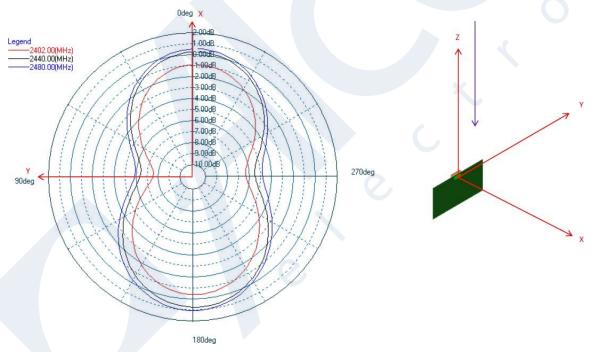

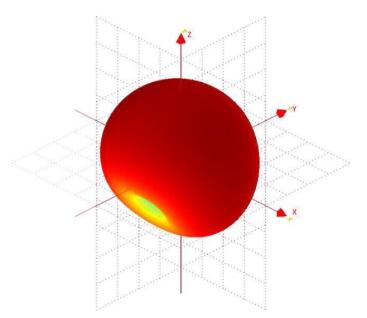

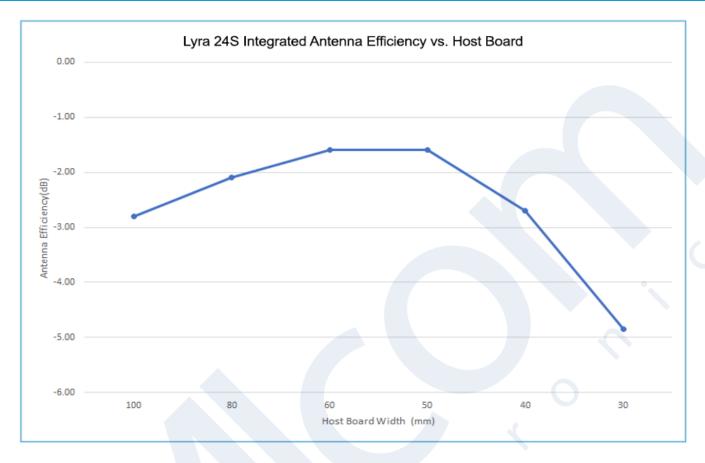

| 4. | .16    | Antenna Radiation and Efficiency for Lyra 24S Integrated Antenna                            | 24 |

| 5  | Refe   | rence Diagrams                                                                              | 27 |

| 5. | .1     | Network Co-Processor (NCP) Application with UART Host                                       | 27 |

| 5. | .2     | SoC Application                                                                             | 28 |

| 5. | .3     | Boot                                                                                        | 28 |

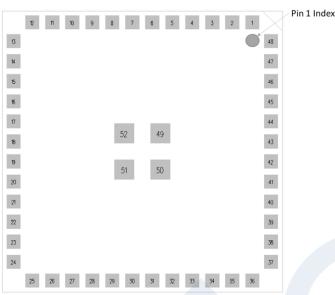

| 6  | Pin D  | Definitions                                                                                 | 29 |

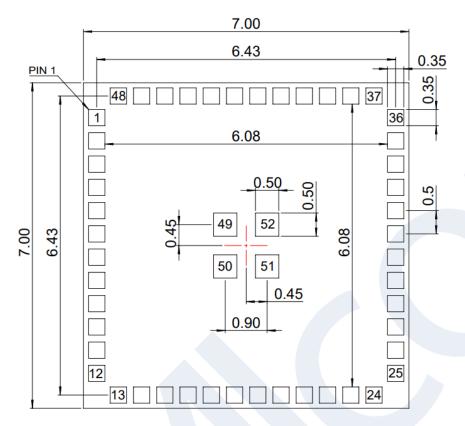

| 6. | .1     | Module Pinout                                                                               | 29 |

| 6. | .2     | Alternate Pin Functions                                                                     | 30 |

|     | 6.3      | Analog Peripheral Connectivity                                                            | 31 |

|-----|----------|-------------------------------------------------------------------------------------------|----|

|     | 6.4      | Digital Peripheral Connectivity                                                           | 31 |

| 7   | Desig    | gn Guidelines                                                                             | 35 |

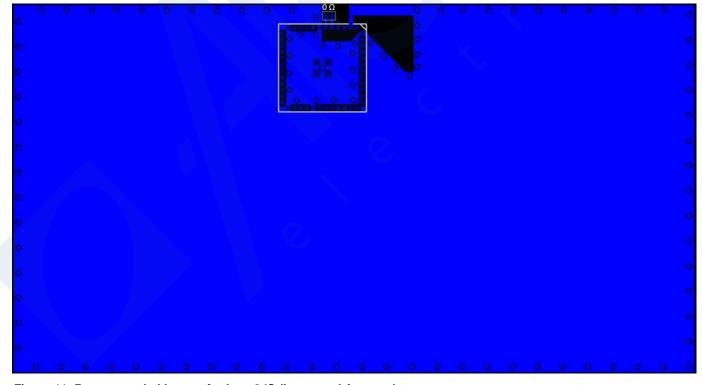

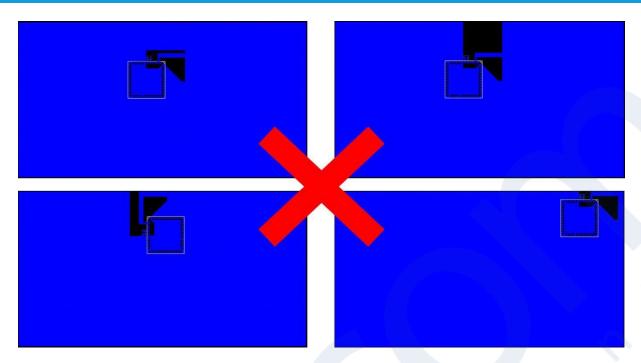

|     | 7.1      | Layout and Placement                                                                      | 35 |

|     | 7.2      | Best Design Practices.                                                                    | 38 |

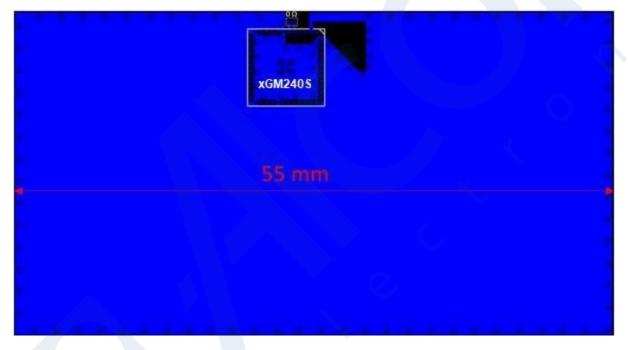

|     | 7.3      | Radio Performance vs. Carrier Board Size                                                  | 39 |

|     | 7.4      | Impact of Human Body and Other Materials in Close Proximity                               | 40 |

|     | 7.5      | Reset                                                                                     | 40 |

|     | 7.6      | Debug                                                                                     | 41 |

|     | 7.7      | Packet Trace Interface (PTI)                                                              | 41 |

|     | 7.8      | Lyra 24S Module 50 Ohms RF Track Design for Connecting External Antenna with the Lyra 24S | 42 |

|     | 7.9      | External Antenna Integration with the Lyra 24S Module 453-00170                           | 45 |

| 8   | Pack     | age Specifications                                                                        | 46 |

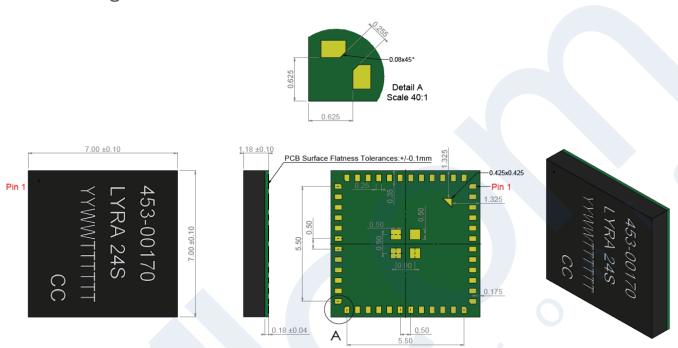

|     | 8.1      | Package Outline                                                                           | 46 |

|     | 8.2      | PCB Land Pattern                                                                          | 47 |

|     | 8.3      | Package Marking                                                                           | 48 |

| 9   | Solde    | ering Recommendations                                                                     | 49 |

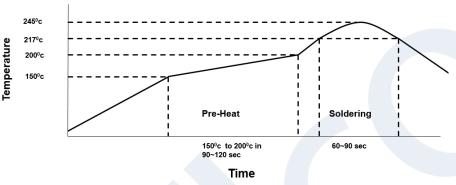

|     | 9.1      | Reflow for lead Free Solder Paste                                                         | 49 |

|     | 9.2      | Recommended Reflow Profile for lead Free Solder Paste                                     | 49 |

| 10  | ) Misce  | ellaneous                                                                                 | 49 |

|     | 10.1     | Cleaning                                                                                  | 49 |

|     | 10.2     | Rework                                                                                    | 49 |

|     | 10.3     | Handling and Storage                                                                      | 50 |

| 11  | Tray     | and Reel                                                                                  | 51 |

| 12  | ? Relia  | bility Test                                                                               |    |

|     | 12.1     | Climatic And Dynamic                                                                      | 52 |

|     | 12.2     | Reliability MTBF Prediction                                                               | 53 |

| 13  | Regu     | ılatory                                                                                   | 53 |

|     | 13.1     | Regulatory information                                                                    | 53 |

|     | 13.2     | Maximum Regulatory Certified RF TX Power per Country (TBD)                                | 53 |

| 14  | Bluet    | tooth SIG Qualification                                                                   | 54 |

|     | 14.1     | Overview                                                                                  | 54 |

| 1 6 | · ^ dd;+ | tional Information                                                                        | 55 |

## 1 Introduction

The Lyra 24S is a secure, high-performance wireless module optimized for the needs of battery and line-powered IoT devices running on Bluetooth networks.

Based on the **Series 2 EFR32BG24 SoC**, it enables Bluetooth® Low Energy connectivity, delivering exceptional RF performance and energy efficiency, industry-leading Se- cure Vault® technology, and future-proofing capabilities.

The Lyra 24S is a complete System in Package solution offered with robust and fully upgradeable software stacks, global regulatory certifications, advanced development and debugging tools, and documentation that simplifies and minimizes the development cycle of your end-product, helping to accelerate its time-to-market.

The Lyra 24S is targeted for a broad range of applications, including:

- Smart Home Devices

- Lighting

- Gateways and Digital Assistants

- Building Automation and Security

## 1.1 Key Features

- Bluetooth Low Energy 5.3

- Bluetooth Mesh connectivity

- Built-in antenna or RF pin

- Up to 10 dBm TX output power (see Maximum Regulatory Certified RF TX Power per Country)

- -97 dBm BLE 1M RX sensitivity

- 32-bit ARM® Cortex®-M33 core running up to 78 MHz

- 1536/256 kB of Flash/RAM memory

- Vault High or Vault Mid security

- Rich set of analog and digital peripherals

- 32 GPIO pins

- -40 to 105 °C

- 7mm x 7mm x 1.18mm

#### 1.2 Hardware Features

### **Supported Protocols**

- Bluetooth Low Energy (BLE) 5.3

- Bluetooth Mesh

- Matter-ready Smart Home Connectivity

#### Wireless System-on-Chip

- 2.4 GHz radio

- TX power up to +10 dBm

- 32-bit ARM Cortex®-M33 with DSP instruction and floating-point unit for efficient signal processing

- 1536 kB flash program memory

- 256 kB RAM data memory

- Embedded Trace Macrocell (ETM) for advanced debugging

#### **Receiver Sensitivity**

- -105.1 dBm (0.1% BER) at 125 kbps GFSK

- -100.7 dBm (0.1% BER) at 500 kbps GFSK

- -97.0 dBm (0.1% BER) at 1 Mbps GFSK

- -94.3 dBm (0.1% BER) at 2 Mbps GFSK

#### **Current Consumption**

- 5.1 mA RX current at 1 Mbps GFSK

- 4.6 mA TX current at 0 dBm

- 23.4 mA TX current at 10 dBm

- 33.4 μA/MHz in Active Mode (EM0) at 39.0 MHz

- 1.3 µA EM2 DeepSleep current (16 kB RAM retention and RTC running from LFRCO)

#### **Regulatory Certification**

- CE (EU)

- UKCA (UK)

- FCC (USA)

- ISED (Canada)

- MIC (Japan)

- KC (South Korea)

- RCM (Australia and New Zealand)

#### **Operating Range**

- 1.8 to 3.8 V

- -40 to +105 °C

#### **Dimensions**

7 mm x 7 mm x 1.18 mm

#### Security

- Secure Boot with Root of Trust and Secure Loader (RTSL)

- Hardware Cryptographic Acceleration with DPA counter- measures for AES128/256, SHA-1, SHA-2 (up to 256-bit), ECC (up to 256-bit), ECDSA, and ECDH

- True Random Number Generator (TRNG) compliant with NIST SP800-90 and AIS-31

- ARM® TrustZone®

- Secure Debug Interface lock/unlock

- Secure Key Management with PUF

- Anti-Tamper

- Secure Attestation

#### **MCU Peripherals**

- Analog to Digital Converter (ADC)

- 12-bit @ 1 Msps

- 16-bit @ 76.9 ksps

- 2 x Analog Comparator (ACMP)

- 2 x Digital to Analog Converter (VDAC)

- Up to 32 General Purpose I/O pins with output state retention and asynchronous interrupts

- 8 Channel DMA Controller

- 16 Channel Peripheral Reflex System (PRS)

- 3 x 16-bit Timer/Counter with 3 Compare/Capture/PWM channels

- 2 x 32-bit Timer/Counter with 3 Compare/Capture/PWM channels

- 2 x 32-bit Real Time Counter (SYSRTC/BURTC)

- 24-bit Low Energy Timer for waveform generation (LETIMER)

- 16-bit Pulse Counter with asynchronous operation (PCNT)

- 2 × Watchdog Timer (WDOG)

- 1 x Universal Synchronous/Asynchronous Receiver/Transmitter (USART), supporting UART/SPI/SmartCard (ISO 7816)/IrDA/I2S

- 2 x Enhanced Universal Synchronous/Asynchronous Receiver/Transmitter (EUSART) supporting UART/SPI/DALI/ IrDA

- $2 \times I^2C$  interface with SMBus support

- Low-Frequency RC Oscillator with precision mode to replace 32 kHz sleep crystal (LFRCO)

- Keypad scanner supporting up to 6x8 matrix (KEYSCAN)

- Die temperature sensor with +/- 1.5 °C accuracy after single-point calibration

All Rights Reserved

#### 1.3 Firmware Options

The Lyra 24S series supports two different firmware options for software development:

AT Command Set - fully featured and extensible to suit any developer's needs.

- Proven over 5+ years

- Basic Bluetooth LE cable replacement

- Simplest implementation possible

C Code - Full software development with Silicon Labs SDK and Toolchain

- Native C code development

- Use Simplicity Studio IDE

- Full functionality of Silicon Labs HW / SW

## **ORDERING INFORMATION**

Table 1: Ordering Information

| Part         | Description                                                                    |

|--------------|--------------------------------------------------------------------------------|

| 453-00170C   | Module, SIP, LYRA 24S, Integrated Antenna (Silicon Labs EFR32BG24) - Cut/Tape  |

| 453-00170R   | Module, SIP, LYRA 24S, Integrated Antenna (Silicon Labs EFR32BG24) - Tape/Reel |

| 453-00170-K1 | Development Kit, SIP, LYRA 24S, Integrated Antenna                             |

#### Note:

- Lyra 24S series modules operate in the 2.4 GHz ISM frequency band (BLE range: 2402-2480MHz).

- The maximum RF TX power allowed by different regional regulatory authorities may differ from the maximum output power a module can produce. End-product manufacturers must then verify that the module is configured to meet the regulatory limits for each region in accordance with the local rules and the formal certification test reports.

- See section Maximum Regulatory Certified RF TX Power per Country.

Lyra 24S modules are pre-programmed with Lyra 24S BGAPI UART/OTA DFU bootloader. Lyra 24S AT firmware can be loaded by the customer (via SWD interface or via boot loader (UART or OTA)).

## 3 SYSTEM OVERVIEW

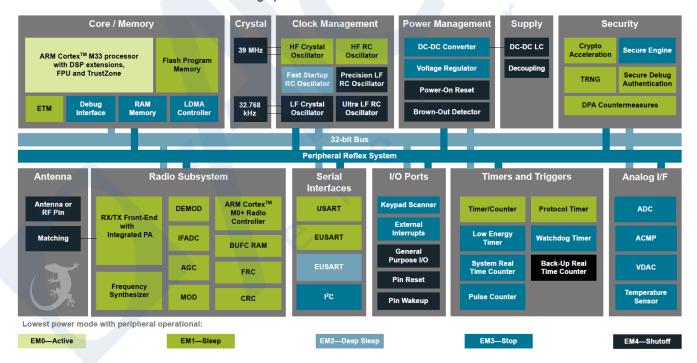

## 3.1 Block Diagram

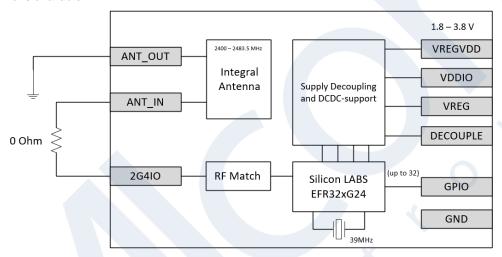

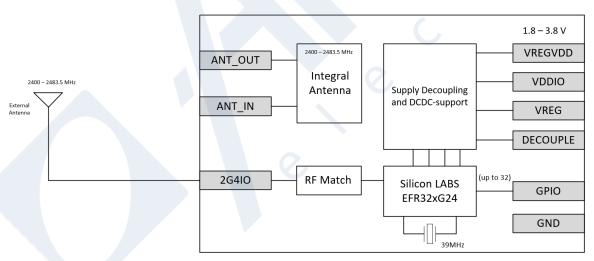

The Lyra 24S module is a highly integrated, high-performance system in package with all the hardware components needed to enable 2.4 GHz wireless connectivity and support robust networking capabilities via multiple wireless protocols.

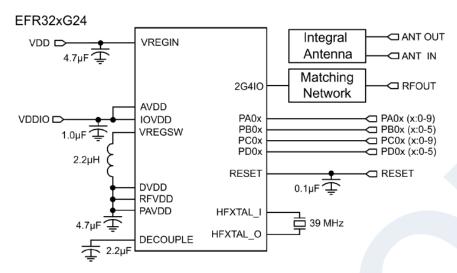

Built around the **EFR32BG24 Wireless SoC**, the Lyra 24S includes a built-in antenna, an RF matching network (optimized for transmit power efficiency), supply decoupling and filtering components, an LC tank for DC-DC conversion, a 39 MHz reference crystal, and an RF shield. Also, it supports the use of an external 32 kHz crystal as a low frequency reference signal via GPIO pins for use cases demanding maximum energy efficiency.

For designs where an external antenna solution may be beneficial, a module variant with a 50  $\Omega$ -matched RF pin instead of the built-in antenna is available.

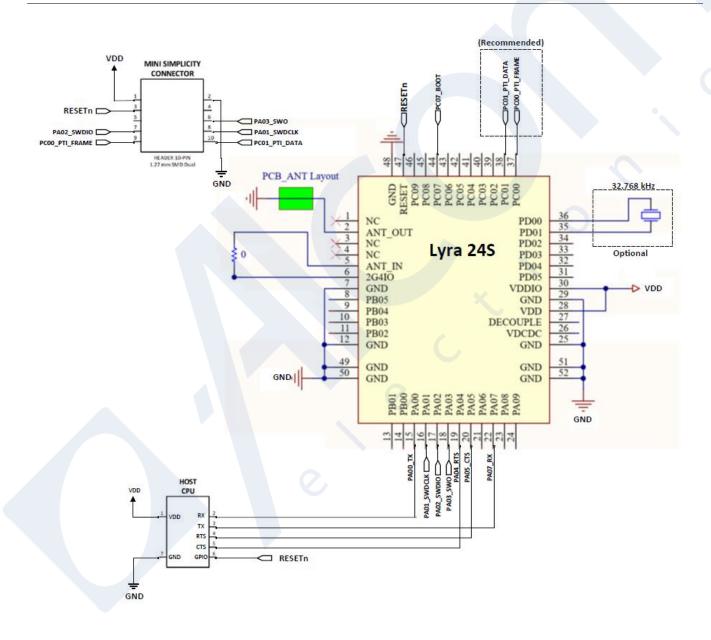

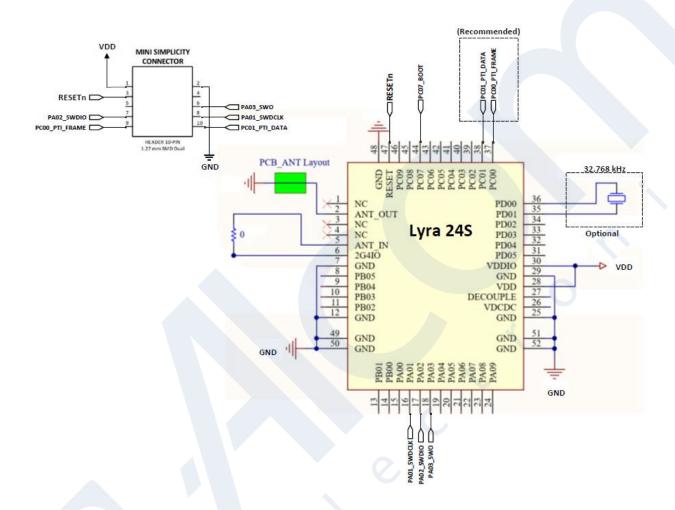

Figure 1: Lyra 24S Block Diagram - Integral Antenna

Figure 2: Lyra 24S Block Diagram - External Antenna

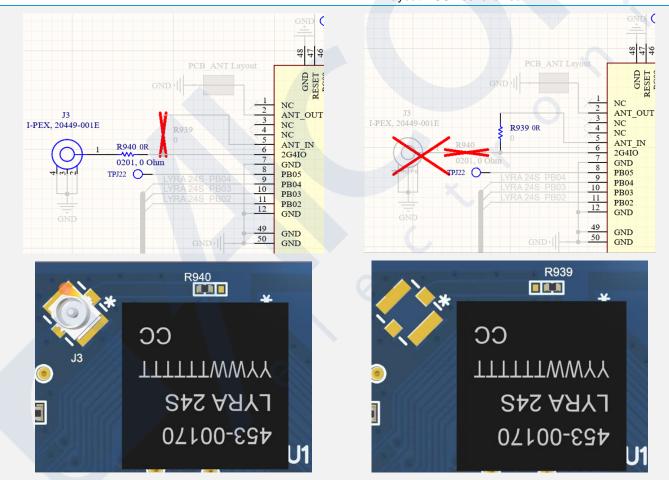

**Note**: There is only one Module, SIP, LYRA 24S, Integrated Antenna (Silicon Labs EFR32BG24) 453-00170, to create the External Antenna connection requires removal of 0R resistor (Figure 1) on customer's board to allow the external antenna to be connected Lyra 24S pin 3 2G4IO (shown in Figure 2). See section Lyra 24S Module 50 Ohms RF Track Design for Connecting External Antenna with the Lyra 24S.

A simplified internal schematic for the Lyra 24S module is shown in Figure 3.

Figure 3: Lyra 24S Module Schematic

## 3.2 EFR32BG24 SoC

The **EFR32BG24 SoC** features a 32-bit ARM Cortex M33 core, a 2.4 GHz high-performance radio, 1536 kB of Flash memory, 256 kB of RAM, a dedicated core for security, a rich set of MCU peripherals, and various clock management and serial interfacing options. See the EFR32xG24 Reference Manual for details.

# 3.3 Integrated Antenna

Lyra 24S modules come with two antenna solution variants: a built-in integral ground loop type antenna realized by a PCB trace design, or a  $50\Omega$ -matched RF pin to support an external antenna. Typical performance characteristics for the built-in antenna are detailed in the table below. See Antenna Radiation and Efficiency for Lyra 24S Integrated Antenna and External Antenna Integration with the Lyra 24S Module 453-00170 for other relevant details.

| Parameter                      | Symbol              | Test Condition                | Min  | Тур | Max    | Unit |

|--------------------------------|---------------------|-------------------------------|------|-----|--------|------|

| Antenna frequency range        | FRANGE              |                               | 2400 | _   | 2483.5 | MHz  |

| Antenna Gain                   | G <sub>MAX</sub>    | Maximum relative to isotropic | _    | _   | 1.48   | dBi  |

| Antenna Efficiency             | Efficiency          |                               | -2.5 | _   | -1.36  | dB   |

| Reference impedance            | Z                   |                               | _    | 50  | _      | Ω    |

| Dielectric Constant Host Board | DI <sub>CONST</sub> |                               | _    | 4.3 | _      |      |

| Trace Thickness                | TTHICKNESS          |                               | _    | 47  | _      | um   |

| VSWR                           | VSWR                | Maximum                       | _    | _   | 2:1    |      |

Antenna efficiency, gain, and radiation pattern are dependent on the application PCB layout and mechanical design. Antenna specification is based on the assumption that the host board design guidelines in section are followed.

## 3.4 External Antenna

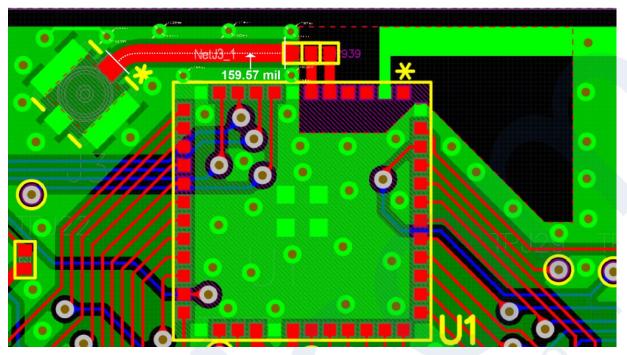

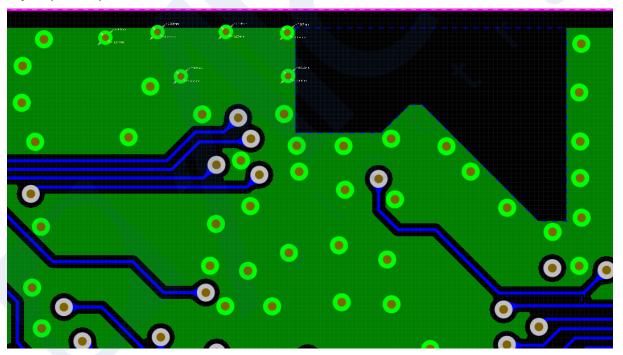

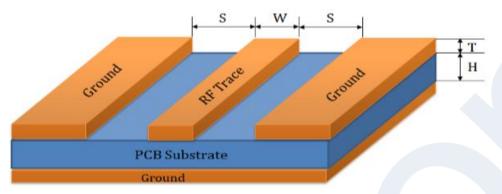

Lyra 24S module can be used with external antennas (certified by Laird Connectivity) and requires a RF 50 Ohm track (Ground Coplanar Waveguide) to be designed to run from Lyra 24S module 2G4IO (pin 6) to an RF antenna connector (IPEX MHF 4) on the host PCB. The 50Ohm RF track design and length **MUST** be copied as defined in section Lyra 24S Module 50 Ohms RF Track Design for Connecting External Antenna with the Lyra 24S.

The list of supported external antennas (certified by Laird Connectivity) are listed in section External Antenna Integration with the Lyra 24S Module.

## 3.5 Power Supply

The Lyra 24S requires a primary supply (VDD) and IO supply (VDDIO) voltage to operate. All necessary decoupling, filtering and DC-DC-related components are included in the module.

# 3.6 General Purpose Input/Output (GPIO)

The Lyra 24S has up to 32 General Purpose Input/Output pins. Each GPIO pin can be individually configured as either an output or input. More advanced configurations including open-drain, open-source, and glitch-filtering can be configured for each individual GPIO pin. The GPIO pins can be overridden by peripheral connections, like SPI communication. Each peripheral connection can be routed to several GPIO pins on the device. The input value of a GPIO pin can be routed through the Peripheral Reflex System to other peripherals. The GPIO subsystem supports asynchronous external pin interrupts.

All of the pins on ports A and port B are EM2 capable. These pins may be used by Low-Energy peripherals in EM2/3 and may also be used as EM2/3 pin wake-ups. Pins on ports C and D are latched/retained in their current state when entering EM2 until EM2 exit upon which internal peripherals could once again drive those pads.

A few GPIOs also have EM4 wake functionality. These pins are listed in Alternate Pin Functions.

## 3.7 Security

Lyra 24S modules support one of two levels in the Security Portfolio offered by Silicon Labs: **Secure Vault Mid** or **Secure Vault High.** Lyra 24S modules support Secure Vault High.

Secure Vault is a collection of technologies that deliver state-of-the-art security and upgradability features to protect and future proof IoT devices against costly threats, attacks, and tampering. A dedicated security CPU enables the Secure Vault functions and isolates cryptographic functions and data from the Cortex-M33 core. Lyra 24S support Secure Vault High.

Table 2: Secure Vault Features

| Feature                                                 | Secure Vault Mid                                                                                             | Secure Vault High                                                                                                      |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| True Random Number Generator (TRNG)                     | Yes                                                                                                          | Yes                                                                                                                    |

| Secure Boot with Root of Trust and Secure Loader (RTSL) | Yes                                                                                                          | Yes                                                                                                                    |

| Secure Debug with Lock/Unlock                           | Yes                                                                                                          | Yes                                                                                                                    |

| DPA Countermeasures                                     | Yes                                                                                                          | Yes                                                                                                                    |

| Anti-Tamper                                             |                                                                                                              | Yes                                                                                                                    |

| Secure Attestation                                      |                                                                                                              | Yes                                                                                                                    |

| Secure Key Management                                   |                                                                                                              | Yes                                                                                                                    |

| Symmetric Encryption                                    | <ul> <li>AES 128 / 192 / 256 bit</li> <li>ECB, CTR, CBC, CFB,<br/>CCM, GCM, CBC-MAC, and<br/>GMAC</li> </ul> | <ul> <li>AES 128 / 192 / 256 bit</li> <li>ECB, CTR, CBC, CFB, CCM, GCM, CBC-MAC, and GMAC</li> <li>ChaCha20</li> </ul> |

| Public Key Encryption - ECDSA / ECDH / EdDSA            | • p192 and p256                                                                                              | <ul><li>p192, p256, p384 and p521</li><li>Curve25519 (ECDH)</li><li>Ed25519 (EdDSA)</li></ul>                          |

| Key Derivation                                          | ■ ECJ-PAKE p192 and p256                                                                                     | <ul> <li>ECJ-PAKE p192, p256, p384, and p521</li> <li>PBKDF2</li> <li>HKDF</li> </ul>                                  |

| Hashes                                                  | <ul><li>SHA-1</li><li>SHA-2/256</li></ul>                                                                    | <ul><li>SHA-1</li><li>SHA-2 256, 384, and 512</li><li>Poly1305</li></ul>                                               |

## 3.7.1 Secure Boot with Root of Trust and Secure Loader (RTSL)

The Secure Boot with RTSL authenticates a chain of trusted firmware that begins from an immutable memory (ROM).

It prevents malware injection, prevents rollback, ensures that only authentic firmware is executed, and protects Over The Air updates. For more information about this feature, see Silicon Labs' AN1218: Series 2 Secure Boot with RTSL.

## 3.7.2 Cryptographic Accelerator

The Cryptographic Accelerator is an autonomous hardware accelerator with Differential Power Analysis (DPA) countermeasures to protect keys.

It supports AES encryption and decryption with 128/192/256-bit keys, ChaCha20 encryption, and Elliptic Curve Cryptography (ECC) to support public key operations, and hashes.

Supported block cipher modes of operation for AES include:

- ECB (Electronic Code Book)

- CTR (Counter Mode)

- CBC (Cipher Block Chaining)

- CFB (Cipher Feedback)

- GCM (Galois Counter Mode)

- CCM (Counter with CBC-MAC)

- CBC-MAC (Cipher Block Chaining Message Authentication Code)

- GMAC (Galois Message Authentication Code)

The Cryptographic Accelerator accelerates Elliptical Curve Cryptography and supports the NIST (National Institute of Standards and Technology) recommended curves including P-192, P-256, P-384, and P-521 for ECDH (Elliptic Curve Diffie-Hellman) key derivation, and ECDSA (Elliptic Curve Digital Signature Algorithm) sign and verify operations. Also supported is the non-NIST Curve25519 for ECDH and Ed25519 for EdDSA (Edwards-curve Digital Signature Algorithm) sign and verify operations.

Secure Vault also supports ECJ-PAKE (Elliptic Curve variant of Password Authenticated Key Exchange by Juggling) and PBKDF2 (Password-Based Key Derivation Function 2).

Supported hashes include SHA-1, SHA-2/256/384/512 and Poly1305.

This implementation provides a fast and energy efficient solution to state of the art cryptographic needs.

## 3.7.3 True Random Number Generator

The True Random Number Generator module is a non-deterministic random number generator that harvests entropy from a thermal energy source. It includes start-up health tests for the entropy source as required by NIST SP800-90B and AIS-31 as well as online health tests required for NIST SP800-90C.

The TRNG is suitable for periodically generating entropy to seed an approved pseudo random number generator.

https://www.lairdconnect.com/ Americas: +1-800-492-2320 © Copyright 2023 Laird Connectivity

## 3.7.4 Secure Debug with Lock/Unlock

For obvious security reasons, it is critical for a product to have its debug interface locked before being released in the field.

In addition, Secure Vault High also provides a secure debug unlock function that allows authenticated access based on public key cryptography. This functionality is particularly useful for supporting failure analysis while maintaining confidentiality of IP and sensitive end-user data.

For more information about this feature, see Silicon Labs' AN1190: Series 2 Secure Debug.

### 3.7.5 DPA Countermeasures

The AES and ECC accelerators have Differential Power Analysis (DPA) countermeasures support. This makes it very expensive from a time and effort standpoint to use DPA to recover secret keys.

## 3.7.6 Secure Key Management with PUF

Key material in Secure Vault High products is protected by "key wrapping" with a standardized symmetric encryption mechanism. This method has the advantage of protecting a virtually unlimited number of keys, limited only by the storage that is accessible by the Cortex-M33, which includes off-chip storage as well. The symmetric key used for this wrapping and unwrapping must be highly secure because it can expose all other key materials in the system. The Secure Vault Key Management system uses a Physically Unclonable Function (PUF) to generate a persistent device-unique seed key on power up to dynamically generate this critical wrapping/unwrapping key which is only visible to the AES encryption engine and is not retained when the device loses power.

## 3.7.7 Anti-Tamper

Secure Vault High devices provide internal tamper protection which monitors parameters such as voltage, temperature, and electro- magnetic pulses as well as detecting tamper of the security sub-system itself. Additionally, 8 external configurable tamper pins support external tamper sources, such as enclosure tamper switches.

For each tamper event, the user is able to select the severity of the tamper response ranging from an interrupt, to a reset, to destroying the PUF reconstruction data which will make all protected key materials un-recoverable and effectively render the device inoperable. The tamper system also has an internal resettable event counter with programmable trigger threshold and refresh periods to mitigate false positive tamper events.

For more information about this feature, see Silicon Labs' AN1247: Anti-Tamper Protection Configuration and Use.

## 3.7.8 Secure Attestation

Secure Vault High products support Secure Attestation, which begins with a secure identity that is created during the Silicon Labs manufacturing process. During device production, each device generates its own public/private keypair and securely stores the wrapped private key into immutable OTP memory and this key never leaves the device. The corresponding public key is extracted from the device and inserted into a binary DER-encoded X.509 device certificate, which is signed into a Silicon Labs CA chain and then programmed back into the chip into an immutable OTP memory.

The secure identity can be used to authenticate the chip at any time in the life of the product. The production certification chain can be requested remotely from the product. This certification chain can be used to verify that the device was authentically produced by Silicon Labs. The device unique public key is also bound to the device certificate in the certification chain. A challenge can be sent to the chip at any point in time to be signed by the device private key. The public key in the device certificate can then be used to verify the challenge response, proving that the device has access to the securely stored private key, which prevents counterfeit products or impersonation attacks.

For more information about this feature, see Silicon Labs' AN1268: Authenticating Silicon Labs Devices Using Device Certificates.

#### **ELECTRICAL SPECIFICATIONS** 4

All electrical parameters in all tables are specified under the following conditions, unless stated otherwise:

- Typical values are based on T<sub>A</sub>=25 °C and VDD = VDDIO = 3.0 V, by production test and/or technology characterization.

- Radio performance numbers are measured in conducted mode, based on Silicon Laboratories reference designs using output power-specific external RF impedance-matching networks for interfacing to a 50  $\Omega$  antenna.

- Minimum and maximum values represent the worst conditions across supply voltage, process variation, and operating temperature, unless stated otherwise.

#### Absolute Maximum Ratings 4.1

Table 3: Absolute Maximum Ratings

| Parameter                             | Symbol                | Test Condition | Min  | Тур | Max                     | Unit |

|---------------------------------------|-----------------------|----------------|------|-----|-------------------------|------|

| Storage temperature range             | T <sub>STG</sub>      |                | -40  | _   | +105                    | °C   |

| Voltage on any supply pin             | $V_{\text{DDMAX}}$    |                | -0.3 |     | 3.8                     | V    |

| Voltage ramp rate on any supply pin   | VDDRAMPMAX            |                |      |     | 1.0                     | V/µs |

| DC voltage on any GPIO pin            | VDIGPIN               |                | -0.3 |     | V <sub>VDDIO</sub> +0.3 | V    |

| DC voltage on RESETn pin <sup>1</sup> | VRESETn               |                | -0.3 |     | 3.8                     | V    |

| Absolute voltage on RFOUT pin         | V <sub>MAX2G4</sub>   |                | -0.3 |     | V <sub>VDD</sub> +0.3   | V    |

| Total current into VDD pin            | $I_{VDDMAX}$          | Source         |      | _   | 200                     | mA   |

| Total current into GND pin            | I <sub>VSSMAX</sub>   | Sink           | _    |     | 200                     | mA   |

| Current per I/O pin                   | I <sub>IOMAX</sub>    | Sink           | _    |     | 50                      | mA   |

|                                       |                       | Source         |      | . — | 50                      | mA   |

| Current for all I/O pins              | I <sub>IOALLMAX</sub> | Sink           |      |     | 200                     | mA   |

|                                       |                       | Source         |      |     | 200                     | mA   |

### Note:

Americas: +1-800-492-2320 Europe: +44-1628-858-940 All Rights Reserved Hong Kong: +852-2762-4823

<sup>1.</sup> The RESETn pin has a pull-up device to the internal DVDD supply. For minimum leakage, RESETn should not exceed the voltage at DVDD, which is generated by the DC-DC converter. DVDD is equal to 1.8 V when DC-DC is active and bypassed to VDD when DC-DC is inactive.

# 4.2 General Operating Conditions

**Table 4: General Operating Conditions**

| Parameter                           | Symbol                   | Test Condition                             | Min  | Тур  | Max  | Unit |

|-------------------------------------|--------------------------|--------------------------------------------|------|------|------|------|

| Operating ambient temperature range | T <sub>A</sub>           |                                            | -40  | _    | +105 | °C   |

| VDD operating supply voltage        | $V_{VDD}$                | DC-DC in regulation                        | 2.2  | 3.0  | 3.8  | V    |

|                                     |                          | DC-DC in bypass                            | 1.8  | 3.0  | 3.8  | V    |

| VDDIO operating supply voltage      | $V_{VDDIO}$              | AVDDBODEN=0,<br>IOVDDxBODEN=0 <sup>1</sup> | 1.71 | 3.0  | 3.8  | V    |

| HCLK and SYSCLK frequency           | f <sub>HCLK</sub>        | VSCALE2, MODE = WS1                        |      |      | 78   | MHz  |

|                                     |                          | VSCALE2, MODE = WS0                        |      |      | 40   | MHz  |

|                                     |                          | VSCALE1, MODE = WS0                        |      | _    | 40   | MHz  |

| EM01 Group A clock frequency        | f <sub>EM01GRPACLK</sub> | VSCALE2                                    |      |      | 78   | MHz  |

|                                     |                          | VSCALE1                                    | _    | _    | 40   | MHz  |

| EM01 Group C clock frequency        | f <sub>EM01GRPCCLK</sub> | VSCALE2                                    |      | _    | 78   | MHz  |

|                                     |                          | VSCALE1                                    | _    |      | 40   | MHz  |

| Radio HCLK frequency                | f <sub>RHCLK</sub>       | VSCALE2 or VSCALE1                         |      | 39.0 |      | MHz  |

|                                     |                          |                                            |      |      |      |      |

#### Note:

# 4.3 MCU Current Consumption at 3.0V

Unless otherwise indicated, typical conditions are: VDD = VDDIO = 3.0 V, DC-DC in regulation. Voltage scaling level = VSCALE1.  $T_A = 25$  °C. Minimum and maximum values in this table represent the worst conditions across process variation at  $T_A = 25$  °C.

Table 5: MCU Current Consumption at 3.0V

| Parameter                                                     | Symbol              | Test Condition                                                                                         | Min | Тур  | Max | Unit   |

|---------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM0 mode with all peripherals disabled | I <sub>ACTIVE</sub> | 78 MHz HFRCO w/ DPLL referenced to<br>39 MHz crystal, CPU running Prime<br>from flash, VSCALE2         | _   | 33.3 | _   | μΑ/MHz |

|                                                               |                     | 78 MHz HFRCO w/ DPLL referenced to<br>39 MHz crystal, CPU running while<br>loop from flash, VSCALE2    | _   | 32.8 | _   | μA/MHz |

|                                                               |                     | 78 MHz HFRCO w/ DPLL referenced<br>to 39 MHz crystal, CPU running<br>CoreMark loop from flash, VSCALE2 | _   | 49.1 | _   | µA/MHz |

|                                                               |                     | 39 MHz crystal, CPU running Prime from flash                                                           | _   | 33.9 | _   | µA/MHz |

|                                                               |                     | 39 MHz crystal, CPU running while loop from flash                                                      | _   | 33.4 | _   | µA/MHz |

|                                                               |                     | 39 MHz crystal, CPU running CoreMark loop from flash                                                   | _   | 49.4 | _   | µA/MHz |

|                                                               |                     | 38 MHz HFRCO, CPU running while loop from flash                                                        | _   | 28.1 | _   | μΑ/MHz |

<sup>1.</sup> The AVDD and IOVDD BOD enable bits are in the EMU\_BOD3SENSE register. These BODs are disabled on reset.

| Parameter                                | Symbol              | Test Condition                                                                                | Min | Тур  | Max | Unit   |

|------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM1 mode with all | I <sub>EM1</sub>    | 78 MHz HFRCO w/ DPLL referenced to 39 MHz crystal, VSCALE2                                    | _   | 22.6 | _   | μΑ/MHz |

| peripherals disabled                     |                     | 39 MHz crystal                                                                                | _   | 24.4 | _   | µA/MHz |

|                                          |                     | 38 MHz HFRCO                                                                                  | _   | 19.0 | _   | µA/MHz |

| Current consumption in EM2 mode, VSCALE0 | I <sub>EM2_VS</sub> | 256 kB RAM and full Radio RAM retention, RTC running from LFXO <sup>1</sup>                   | _   | 3.1  | _   | μΑ     |

|                                          |                     | 256 kB RAM and full Radio RAM retention, RTC running from LFRCO <sup>1</sup>                  | - / | 3.1  | -   | μΑ     |

|                                          |                     | 16 kB RAM and full Radio RAM retention, RTC running from LFXO <sup>1</sup>                    |     | 1.3  | _   | μΑ     |

|                                          |                     | 16 kB RAM and full Radio RAM retention, RTC running from LFRCO <sup>1</sup>                   | -   | 1.3  | _   | μΑ     |

|                                          |                     | 16 kB RAM and full Radio RAM retention, RTC running from LFRCO in precision mode <sup>1</sup> |     | 1.9  | _   | μΑ     |

| Current consumption in EM3 mode, VSCALE0 | I <sub>EM3_VS</sub> | 256 kB RAM and full Radio RAM retention, RTC running from ULFRCO <sup>1</sup>                 | -   | 2.9  | 1   | μΑ     |

|                                          |                     | 16 kB RAM and full Radio RAM retention, RTC running from ULFRCO <sup>1</sup>                  | _   | 1.1  | _   | μΑ     |

| Current consumption in EM4 mode          | I <sub>EM4</sub>    | No BURTC, no LF oscillator                                                                    |     | 0.31 |     | μΑ     |

|                                          |                     | BURTC with LFXO                                                                               | _   | 0.64 | _   | μΑ     |

| Current consumption during reset         | I <sub>RST</sub>    | Hard pin reset held                                                                           | ×-  | 467  | _   | μΑ     |

### Note:

1. CPU cache retained, EM0/1 peripheral states retained

https://www.lairdconnect.com/

# Radio Current Consumption with 3.0 V Supply

RF current consumption measured with MCU in EM1 and all MCU peripherals disabled. Unless otherwise indicated, typical conditions are: VDD = VDDIO = 3.0 V, DC-DC in regulation.  $T_A = 25 \,^{\circ}\text{C}$ .

Table 6: Radio Current Consumption with 3.0 V Supply

| Parameter                            | Symbol                 | Test Condition                       | Min | Тур  | Max | Unit |

|--------------------------------------|------------------------|--------------------------------------|-----|------|-----|------|

| Current consumption in               | I <sub>RX_ACTIVE</sub> | 125 kbit/s, 2GFSK, f = 2.4 GHz       |     | 5.4  |     | mA   |

| receive mode, active packet          |                        | 500 kbit/s, 2GFSK, f = 2.4 GHz       |     | 5.5  | _   | mA   |

| reception, VSCALE1, EM1P             |                        | 1 Mbit/s, 2GFSK, f = 2.4 GHz         |     | 5.1  | _   | mA   |

|                                      |                        | 2 Mbit/s, 2GFSK, f = 2.4 GHz         |     | 5.8  | _   | mΑ   |

| Current consumption in receive       | I <sub>RX_LISTEN</sub> | 125 kbit/s, 2GFSK, f = 2.4 GHz       |     | 5.4  |     | mΑ   |

| mode, listening for packet,          |                        | 500 kbit/s, 2GFSK, f = 2.4 GHz       |     | 5.4  |     | mA   |

| VSCALE1, EM1P                        |                        | 1 Mbit/s, 2GFSK, f = 2.4 GHz         |     | 5.0  |     | mA   |

|                                      |                        | 2 Mbit/s, 2GFSK, f = 2.4 GHz         |     | 5.8  |     | mA   |

| Current consumption in transmit mode | I <sub>TX</sub>        | f = 2.4 GHz, CW, 10 dBm output power |     | 23.4 |     | mA   |

## RF Transmitter General Characteristics for the 2.4 GHz Band

Unless otherwise indicated, typical conditions are: VDD = VDDIO = 3.0 V, DC-DC in regulation. RF center frequency 2.45 GHz.  $T_A = 25$ °C.

Table 7: RF Transmitter General Characteristics for the 2.4 GHz Band

| Parameter                                                         | Symbol                | Test Condition                                                 | Min      | Тур   | Max  | Unit |

|-------------------------------------------------------------------|-----------------------|----------------------------------------------------------------|----------|-------|------|------|

| RF tuning frequency range                                         | F <sub>RANGE</sub>    |                                                                | 2402     | _     | 2480 | MHz  |

| Maximum TX power                                                  | POUT <sub>MAX</sub>   | 10 dBm                                                         | _        | 10.0  |      | dBm  |

|                                                                   |                       | 0 dBm                                                          | <u> </u> | -1.4  |      | dBm  |

| Minimum active TX power                                           | POUT <sub>MIN</sub>   | 10 dBm                                                         | _        | -29.1 | _    | dBm  |

|                                                                   |                       | 0 dBm                                                          | _        | -24.9 |      | dBm  |

| Output power step size                                            | POUT <sub>STEP</sub>  | 0 dBm                                                          | 0.1      | 0.6   | 10   | dB   |

|                                                                   | -                     | 10 dBm, -5 dBm < Output power < 0 dBm                          | 0.2      | 0.7   | 1.7  | dB   |

|                                                                   |                       | 10 dBm, 0 dBm < Output power < 10 dBm                          | 0.04     | 0.2   | 0.8  | dB   |

| Output power variation vs supply voltage variation,               | POUT <sub>VAR_V</sub> | 10 dBm output power with VDD voltage swept from 1.8 V to 3.8 V | _        | 0.02  | _    | dB   |

| frequency = 2450 MHz                                              |                       | 0 dBm output power with VDD voltage swept from 1.8 V to 3.8 V  | _        | 0.06  | _    | dB   |

| Output power variation vs<br>temperature, Frequency =<br>2450 MHz | POUT <sub>VAR_T</sub> | 0 dBm, (-40 to +105 °C)                                        | _        | 1.1   | _    | dB   |

| Output power variation over                                       | $POUT_{VAR_{F}}$      | 10 dBm                                                         | _        | 0.6   | _    | dB   |

| the RF tuning frequency range                                     |                       | 0 dBm                                                          | _        | 0.07  | _    | dB   |

Hong Kong: +852-2762-4823

## 4.6 RF Receiver General Characteristics for the 2.4 GHz Band

Unless otherwise indicated, typical conditions are: VDD = VDDIO = 3.0 V, DC-DC in regulation. RF center frequency 2.45 GHz.  $T_A = 25^{\circ}C$ .

Table 8: RF Receiver General Characteristics for the 2.4 GHz Band

| Parameter                 | Symbol             | Test Condition | Min  | Тур | Max  | Unit |

|---------------------------|--------------------|----------------|------|-----|------|------|

| RF tuning frequency range | F <sub>RANGE</sub> |                | 2402 |     | 2480 | MHz  |

# 4.7 RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 1 Mbps Data Rate

Unless otherwise indicated, typical conditions are: VDD = VDDIO = 3.0 V, DC-DC in regulation. RF center frequency 2.45 GHz.  $T_A = 25^{\circ}C$ .

Table 9: RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 1 Mbps Data Rate

| Parameter                                        | Symbol              | Test Condition                                                                              | Min | Тур   | Max | Unit |

|--------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------|-----|-------|-----|------|

| Rx Max Strong Signal Input<br>Level for 0.1% BER | RX <sub>SAT</sub>   | Signal is reference signal <sup>1</sup>                                                     |     | 10    | _   | dBm  |

| Sensitivity                                      | SENS                | Signal is reference signal, 37 byte payload <sup>1</sup>                                    | _   | -97   |     | dBm  |

|                                                  |                     | Signal is reference signal, 255 byte payload <sup>1</sup>                                   | _   | -95.4 | _   | dBm  |

|                                                  |                     | With non-ideal signals <sup>2</sup>                                                         |     | -95.0 | _   | dBm  |

| Signal to co-channel interferer                  | C/I <sub>CC</sub>   | (see notes) <sup>1 3</sup>                                                                  | _   | 8.7   | _   | dB   |

| N ± 1 Adjacent channel selectivity               | C/I <sub>1</sub>    | Interferer is reference signal at +1 MHz offset <sup>1 4 3 5</sup>                          | _   | -5.4  | _   | dB   |

|                                                  |                     | Interferer is reference signal at -1 MHz offset <sup>1 4 3 5</sup>                          | _   | -5.3  | _   | dB   |

| N ± 2 Alternate channel selectivity              | C/I <sub>2</sub>    | Interferer is reference signal at +2 MHz offset <sup>1 4 3 5</sup>                          | _   | -40.9 | _   | dB   |

|                                                  |                     | Interferer is reference signal at -2 MHz offset <sup>1 4 3 5</sup>                          | _   | -39.7 | _   | dB   |

| N ± 3 Alternate channel selectivity              | C/I <sub>3</sub>    | Interferer is reference signal at +3 MHz offset <sup>1 4 3 5</sup>                          | _   | -45.5 | _   | dB   |

|                                                  |                     | Interferer is reference signal at -3 MHz offset <sup>1 4 3 5</sup>                          | _   | -45.7 | _   | dB   |

| Selectivity to image frequency                   | C/I <sub>IM</sub>   | Interferer is reference signal at image frequency with 1 MHz precision 15                   | _   | -23.3 | _   | dB   |

| Selectivity to image frequency ± 1 MHz           | C/I <sub>IM_1</sub> | Interferer is reference signal at image frequency +1 MHz with 1 MHz precision <sup>1</sup>  | _   | -40.9 | _   | dB   |

|                                                  |                     | Interferer is reference signal at image frequency -1 MHz with 1 MHz precision <sup>15</sup> | _   | -5.4  | _   | dB   |

| Intermodulation performance                      | IM                  | n = 3 (see note <sup>6</sup> )                                                              | _   | -17.3 | _   | dBm  |

|                                                  |                     | ·                                                                                           |     |       |     |      |

| Parameter | Symbol | Test Condition | Min | Тур | Max | Unit |

|-----------|--------|----------------|-----|-----|-----|------|

| Note:     |        |                |     |     |     |      |

- 1.0.017% Bit Error Rate.

- 2. With non-ideal signals as specified in Bluetooth Test Specification RF-PHY.TS.5.0.1 section 4.7.1

- 3. Desired signal -67 dBm.

- 4. Desired frequency 2402 MHz ≤ Fc ≤ 2480 MHz.

- 5. With allowed exceptions.

- 6. As specified in Bluetooth Core specification version 5.1, Vol 6, Part A, Section 4.4

# 4.8 RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 2 Mbps Data Rate

Unless otherwise indicated, typical conditions are: VDD = VDDIO = 3.0 V, DC-DC in regulation. RF center frequency 2.45 GHz.  $T_A = 25^{\circ}C$ .

Table 10: RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 2 Mbps Data Rate

| Parameter                                        | Symbol              | Test Condition                                                                               | Min | Тур   | Max           | Unit |

|--------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------|-----|-------|---------------|------|

| Rx Max Strong Signal Input<br>Level for 0.1% BER | RX <sub>SAT</sub>   | Signal is reference signal <sup>1</sup>                                                      |     | 10    | $\overline{}$ | dBm  |

| Sensitivity                                      | SENS                | Signal is reference signal, 37 byte payload <sup>1</sup>                                     | _   | -94.3 |               | dBm  |

|                                                  |                     | Signal is reference signal, 255 byte payload <sup>1</sup>                                    | _   | -92.7 | _             | dBm  |

|                                                  |                     | With non-ideal signals <sup>2</sup> 1                                                        | 4   | -92.5 | _             | dBm  |

| Signal to co-channel interferer                  | C/I <sub>CC</sub>   | (see notes) <sup>1 3</sup>                                                                   | _   | 8.6   | _             | dB   |

| N ± 1 Adjacent channel selectivity               | C/I <sub>1</sub>    | Interferer is reference signal at +2 MHz offset <sup>1 4 3 5</sup>                           | _   | -5.3  | _             | dB   |

|                                                  |                     | Interferer is reference signal at -2 MHz offset <sup>1 4 3 5</sup>                           | _   | -5.8  | _             | dB   |

| N ± 2 Alternate channel selectivity              | C/I <sub>2</sub>    | Interferer is reference signal at +4 MHz offset <sup>1 4 3 5</sup>                           | _   | -42.2 | _             | dB   |

|                                                  |                     | Interferer is reference signal at -4 MHz offset 1 4 3 5                                      | _   | -44.2 | _             | dB   |

| N ± 3 Alternate channel selectivity              | C/I <sub>3</sub>    | Interferer is reference signal at +6 MHz offset <sup>1 4 3 5</sup>                           | _   | -48.1 | _             | dB   |

|                                                  |                     | Interferer is reference signal at -6 MHz offset 1 4 3 5                                      | _   | -50.2 | _             | dB   |

| Selectivity to image frequency                   | C/I <sub>IM</sub>   | Interferer is reference signal at image frequency with 1 MHz precision <sup>1 5</sup>        | _   | -22.8 | _             | dB   |

| Selectivity to image frequency ± 2 MHz           | C/I <sub>IM_1</sub> | Interferer is reference signal at image frequency +2 MHz with 1 MHz precision <sup>1 5</sup> | _   | -42.2 | _             | dB   |

|                                                  |                     | Interferer is reference signal at image frequency -2 MHz with 1 MHz precision <sup>1</sup>   | _   | -5.3  | -             | dB   |

| Intermodulation performance                      | IM                  | n = 3 (see note <sup>6</sup> )                                                               | _   | -18.3 | _             | dBm  |

|                                                  |                     |                                                                                              |     |       |               |      |

| Parameter | Symbol | Test Condition | Min | Тур | Max | Unit |

|-----------|--------|----------------|-----|-----|-----|------|

| Note:     |        |                |     |     |     |      |

- 1.0.017% Bit Error Rate.

- 2. With non-ideal signals as specified in Bluetooth Test Specification RF-PHY.TS.5.0.1 section 4.7.1

- 3. Desired signal -64 dBm.

- 4. Desired frequency 2402 MHz ≤ Fc ≤ 2480 MHz.

- 5. With allowed exceptions.

- 6. As specified in Bluetooth Core specification version 5.1, Vol 6, Part A, Section 4.4

# 4.9 RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 500 kbps Data Rate

Unless otherwise indicated, typical conditions are: VDD = VDDIO = 3.0 V, DC-DC in regulation. RF center frequency 2.45 GHz.  $T_A = 25^{\circ}C$ .

Table 11: RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 500 kbps Data Rate

| Parameter                                           | Symbol              | Test Condition                                                                               | Min | Тур    | Max            | Unit |

|-----------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------|-----|--------|----------------|------|

| Rx Max Strong Signal<br>Input Level for 0.1%<br>BER | RX <sub>SAT</sub>   | Signal is reference signal <sup>1</sup>                                                      |     | 10     | $\overline{C}$ | dBm  |

| Sensitivity                                         | SENS                | Signal is reference signal, 37 byte payload <sup>1</sup>                                     | _   | -100.7 | _              | dBm  |

|                                                     |                     | Signal is reference signal, 255 byte payload <sup>1</sup>                                    | _   | -99.4  | _              | dBm  |

|                                                     |                     | With non-ideal signals <sup>2</sup> 1                                                        | \   | -98.4  | _              | dBm  |

| Signal to co-channel interferer                     | C/I <sub>CC</sub>   | (see notes) <sup>1 3</sup>                                                                   | _   | 2.7    | _              | dB   |

| N ± 1 Adjacent channel selectivity                  | C/I <sub>1</sub>    | Interferer is reference signal at +1 MHz offset <sup>1 4 3 5</sup>                           | _   | -7.1   | _              | dB   |

|                                                     |                     | Interferer is reference signal at -1 MHz offset <sup>1 4 3 5</sup>                           | _   | -7.4   | _              | dB   |

| N ± 2 Alternate channel selectivity                 | C/I <sub>2</sub>    | Interferer is reference signal at +2 MHz offset <sup>1 4 3 5</sup>                           | _   | -46.8  | _              | dB   |

|                                                     |                     | Interferer is reference signal at -2 MHz offset <sup>1 4 3 5</sup>                           | _   | -49.7  | _              | dB   |

| N ± 3 Alternate channel selectivity                 | C/I <sub>3</sub>    | Interferer is reference signal at +3 MHz offset <sup>1 4 3 5</sup>                           | _   | -49.4  | _              | dB   |

|                                                     |                     | Interferer is reference signal at -3 MHz offset <sup>1 4 3 5</sup>                           | _   | -54.5  | _              | dB   |

| Selectivity to image frequency                      | C/I <sub>IM</sub>   | Interferer is reference signal at image frequency with 1 MHz precision 15                    | _   | -49    | _              | dB   |

| Selectivity to image frequency ± 1 MHz              | C/I <sub>IM_1</sub> | Interferer is reference signal at image frequency +1 MHz with 1 MHz precision <sup>1 5</sup> | _   | -49.4  | _              | dB   |

|                                                     |                     | Interferer is reference signal at image frequency -1 MHz with 1 MHz precision <sup>1</sup>   | _   | -46.8  | _              | dB   |

| Parameter | Symbol | Test Condition | Min | Тур | Max | Unit |

|-----------|--------|----------------|-----|-----|-----|------|

| Note:     |        |                |     |     |     |      |

- 1.0.017% Bit Error Rate.

- 2. With non-ideal signals as specified in Bluetooth Test Specification RF-PHY.TS.5.0.1 section 4.7.1

- 3. Desired signal -72 dBm.

- 4. Desired frequency 2402 MHz ≤ Fc ≤ 2480 MHz.

- 5. With allowed exceptions.

# 4.10 RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 125 kbps Data Rate

Unless otherwise indicated, typical conditions are: VDD = VDDIO = 3.0 V, DC-DC in regulation. RF center frequency 2.45 GHz.  $T_A = 25^{\circ}C$ .

Table 12: RF Receiver Characteristics for Bluetooth Low Energy in the 2.4 GHz Band 125 kbps Data Rate

| Parameter                                           | Symbol              | Test Condition                                                                                     | Min | Тур    | Max | Unit |

|-----------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------|-----|--------|-----|------|

| Rx Max Strong Signal<br>Input Level for 0.1%<br>BER | RX <sub>SAT</sub>   | Signal is reference signal <sup>1</sup>                                                            |     | 10     | _   | dBm  |

| Sensitivity                                         | SENS                | Signal is reference signal, 37 byte payload <sup>1</sup>                                           |     | -105.1 |     | dBm  |

|                                                     |                     | Signal is reference signal, 255 byte payload <sup>1</sup>                                          | _   | -104.7 | _   | dBm  |

|                                                     |                     | With non-ideal signals <sup>2</sup>                                                                |     | -104.3 |     | dBm  |

| Signal to co-channel interferer                     | C/I <sub>CC</sub>   | (see notes) <sup>1 3</sup>                                                                         | -(  | 0.9    | _   | dB   |

| N ± 1 Adjacent channel selectivity                  | C/I <sub>1</sub>    | Interferer is reference signal at +1 MHz offset <sup>1 4 3 5</sup>                                 | _   | -12.4  | _   | dB   |

|                                                     |                     | Interferer is reference signal at -1 MHz offset <sup>1</sup> 4 3 5                                 | _   | -12.8  | _   | dB   |

| N ± 2 Alternate channel selectivity                 | C/l <sub>2</sub>    | Interferer is reference signal at +2 MHz offset <sup>1 4 3 5</sup>                                 | _   | -52.6  | _   | dB   |

|                                                     |                     | Interferer is reference signal at -2 MHz offset <sup>1</sup> 4 3 5                                 | _   | -55.5  | _   | dB   |

| N ± 3 Alternate channel selectivity                 | C/I <sub>3</sub>    | Interferer is reference signal at +3 MHz offset <sup>1 4 3 5</sup>                                 | _   | -53.8  | _   | dB   |

|                                                     |                     | Interferer is reference signal at -3 MHz offset <sup>1</sup> 4 3 5                                 | _   | -60    | _   | dB   |

| Selectivity to image frequency                      | C/I <sub>IM</sub>   | Interferer is reference signal at image frequency with 1 MHz precision 15                          | _   | -53    | _   | dB   |

| Selectivity to image frequency ± 1 MHz              | C/I <sub>IM_1</sub> | Interferer is reference signal at image<br>frequency +1 MHz with 1<br>MHz precision <sup>1 5</sup> | _   | -53.8  | _   | dB   |

|                                                     |                     | Interferer is reference signal at image frequency -1 MHz with 1 MHz precision 15                   | _   | -52.6  | _   | dB   |

| Parameter | Symbol | Test Condition | Min | Тур | Max | Unit |

|-----------|--------|----------------|-----|-----|-----|------|

|           |        |                |     |     |     |      |

#### Note:

- 1. 0.017% Bit Error Rate.

- 2. With non-ideal signals as specified in Bluetooth Test Specification RF-PHY.TS.5.0.1 section 4.7.1

- 3. Desired signal -79 dBm.

- 4. Desired frequency 2402 MHz ≤ Fc ≤ 2480 MHz.

- 5. With allowed exceptions.

# 4.11 High-Frequency Crystal

Table 13: High-Frequency Crystal

| Parameter                   | Symbol                  | Test Condition                     | Min | Тур | Max | Unit |

|-----------------------------|-------------------------|------------------------------------|-----|-----|-----|------|

| Crystal frequency           | f <sub>HFXTAL</sub>     |                                    | _   | 39  | _   | MHz  |

| Initial calibrated accuracy | $ACC_{HFXTAL}$          |                                    | -5  | _   | +5  | ppm  |

| Temperature drift           | DRIFT <sub>HFXTAL</sub> | Across specified temperature range | -30 | _   | 30  | ppm  |

# 4.12 Low-Frequency Crystal Oscillator

Table 14: Low Frequency Crystal Oscillator

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Symbol               | Test Condition                                                                                | Min  | Тур    | Max  | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------|------|--------|------|------|

| Crystal Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | F <sub>LFXO</sub>    |                                                                                               | _    | 32.768 | _    | kHz  |

| Supported Crystal equivalent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ESR <sub>LFXO</sub>  | GAIN = 0                                                                                      | ,    |        | 80   | kΩ   |

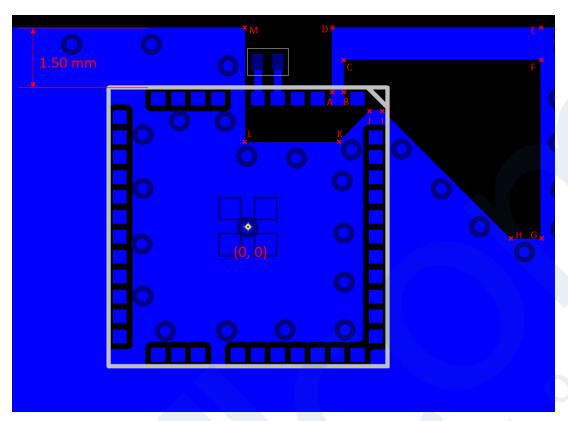

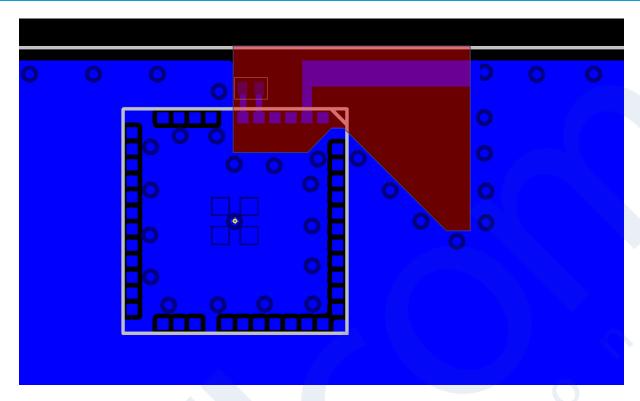

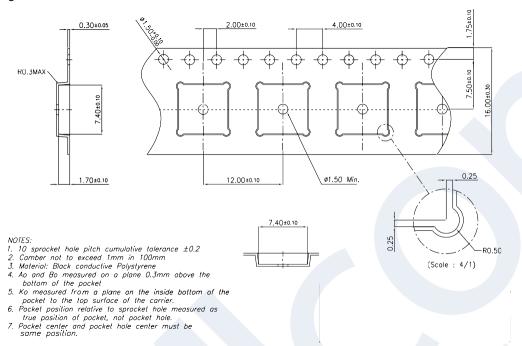

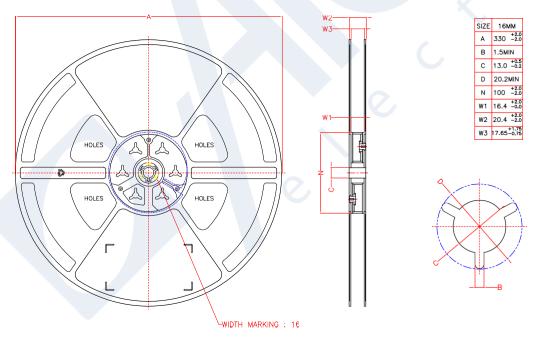

| series resistance (ESR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      | GAIN = 1 to 3                                                                                 |      | _      | 100  | kΩ   |