# CA-IF4988S 3V to 5.5V Half-Duplex RS-485 Transceiver with ±30kV ESD Rating, ±65V Fault Protection, ±40V CMR and Bus Polarity Control

#### 1 Key Features

- Meets or Exceeds the Requirements of the TIA/EIA-485A Standard

- Low EMI 2Mbps Data Rate

- 3V to 5.5V Supply Voltage

- Polarity Control Pin: POL

- Driving POL to Low, Default Bus Polarity

- Driving POL to High, Bus Polarity is Swapped

- Driver with Current Limiter and Thermal Shutdown Protection

- Bus Pins ESD Protection

- ±30kV HBM ESD

- ±6kV IEC 61000-4-2 Contact Discharge

- 1/8 Unit Load (Up to 256 Bus Nodes)

- Open, Short and Idle Bus Failsafe Protection

- Hot Plug-in Protection

- Extended Industrial Temperature Range: –40°C to 125°C

- ±65V Fault Protection on Bus Pins

- ±40V Common Mode Range on Bus Pins

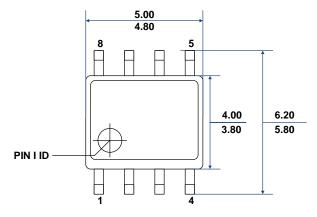

- Standard SOIC8 Narrow Body Package

#### 2 Applications

- HVAC

- Home and Building Automation

- Motion Controllers

- Industrial Automation

- Elevator Control

- Video Surveillance

- Power Grid Infrastructure

#### 3 Description

The CA-IF4988S is the high-performance half-duplex RS-485 transceiver which could be used in harsh industrial and home-appliance environments. The bus pins could withstand high-level ESD events to protect internal circuit without damage.

This device has  $\pm 65V$  fault protection on bus pins, and the common-mode range (CMR) could be extended to  $\pm 40V$

Singel 3 | B-2550 Kontich | Belgium | Tel. +32 (0)3 458 30 33 | info@alcom.be | www.alcom.be Rivium 1e straat 52 | 2909 LE Capelle aan den Ijssel | The Netherlands | Tel. +31 (0)10 288 25 00 | info@alcom.nl | www.alcom.nl

when  $V_{cc}$  ranges from 4.5V to 5.5V, which is suitable for long-cable communication applications. Each device contains one driver and one receiver, supporting the power supply range from 3V to 5.5V. This device could select the polarity of bus pins A/B by the polarity control pin (POL), allowing for software correction of cross-wired field cables through the external controller.

The CA-IF4988S features slew-rate-limited driver for low EMI and date rates up to 2Mbps. This device integrates failsafe circuit to guarantee a logical high on the receiver output when the bus inputs are open, short or on idle state (POL is low). This device features a 1/8 unit load input impedance, allowing up to 256 transceivers on a bus.

The CA-IF4988S devices are packaged in narrow body, 8-pin SOIC packages and specified over ambient free-air temperature range of -40°C to 125°C.

#### **Device Information**

| PART<br>NUMBER | PACKAGE   | BODY SIZE (NOM) |

|----------------|-----------|-----------------|

| CA-IF4988S     | SOIC8 (S) | 3.9mm × 4.9mm   |

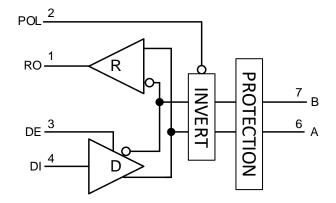

#### **Simplified Schematic**

Copyright © 2024, Chipanalog Incorporated 上海川土徹电子有限公司

## CA-IF4988S

Version 1.00

#### Shanghai Chipanalog Microelectronics Co., Ltd.

#### 4 Ordering Guide

#### Table 4-1 Ordering Guide for Valid Ordering Part Number

| Part Number | Full/Half-Duplex | Date Rate (Mbps) | Package   |

|-------------|------------------|------------------|-----------|

| CA-IF4988S  | Half-Duplex      | 2                | SOIC8 (S) |

# **Table of Contents**

| 1 | Key Fe | eatures                               | 1  |

|---|--------|---------------------------------------|----|

| 2 | Applic | cations                               | 1  |

| 3 | Descri | ption                                 | 1  |

| 4 | Order  | ing Guide                             | 2  |

| 5 | Revisi | on History                            | 3  |

| 6 | Pin De | escriptions and Functions             | 4  |

| 7 | Specif | ications                              | 5  |

|   | 7.1    | Absolute Maximum Ratings <sup>1</sup> | 5  |

|   | 7.2    | ESD Ratings                           | 5  |

|   | 7.3    | Recommended Operating Conditions      | 5  |

|   | 7.4    | Thermal Information                   | 5  |

|   | 7.5    | Electrical Characteristics            | 6  |

|   | 7.6    | Timing Characteristics                | 7  |

|   | 7.7    | Typical Characteristics               | 8  |

| 8 | Param  | neter Measurement Information         | 10 |

| 9 | Detail | ed Description                        | 12 |

|          | 9.1 De                                                | vice Feature Description12                                              |

|----------|-------------------------------------------------------|-------------------------------------------------------------------------|

|          | 9.1.1                                                 | $\pm$ 65V fault protection on Bus Pins                                  |

|          | 9.1.2                                                 | $\pm$ 40V Common-Mode Range12                                           |

|          | 9.1.3                                                 | Bus Failsafe Protection12                                               |

|          | 9.1.4                                                 | Hot Plug-in Protection12                                                |

|          | 9.1.5                                                 | Thermal Shutdown Protection12                                           |

|          | 9.2 De                                                | vice Function Mode12                                                    |

|          | 9.2.1                                                 | Driver                                                                  |

|          | 9.2.2                                                 | Receiver13                                                              |

|          |                                                       |                                                                         |

| 10       | Арр                                                   | ication and Implementation14                                            |

| 10       |                                                       | ication and Implementation14 pical Application14                        |

| 10       | 10.1 Ty                                               |                                                                         |

| 10<br>11 | 10.1 Ty<br>10.2 Pc                                    | pical Application14                                                     |

|          | 10.1 Ty<br>10.2 Pc<br>Pack                            | pical Application14<br>wer Supply Recommendation                        |

|          | 10.1 Ty<br>10.2 Pc<br><b>Pack</b><br>11.1 SC          | pical Application14<br>wer Supply Recommendation14<br>age Information15 |

| 11       | 10.1 Ty<br>10.2 Pc<br>Pack<br>11.1 SC<br>Sold         | pical Application                                                       |

| 11<br>12 | 10.1 Ty<br>10.2 Pc<br>Pack<br>11.1 SC<br>Sold<br>Tape | pical Application                                                       |

#### 5 Revision History

| Revision     | Description | Date       | Page |

|--------------|-------------|------------|------|

| Version 1.00 | NA          | 2024.06.30 | NA   |

CA-IF4988S Version 1.00

Shanghai Chipanalog Microelectronics Co., Ltd.

CHIPANA

ÖG

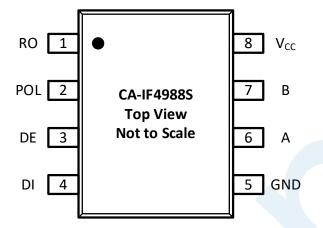

#### 6 Pin Descriptions and Functions

#### Table 6-1 CA-IF4988S Pin Description and Functions

| NAME            | PIN NUMBER | ТҮРЕ             | DESCRIPTION                                                                      |  |  |  |

|-----------------|------------|------------------|----------------------------------------------------------------------------------|--|--|--|

| RO              | 1          | Digital Output   | Receiver data output.                                                            |  |  |  |

|                 |            |                  | Bus polarity control, pulled down internally:                                    |  |  |  |

| POL             | 2          | Digital Input    | 1. When POL is low or open, bus polarity is default;                             |  |  |  |

|                 |            |                  | 2. When POL is high, bus polarity inverts.                                       |  |  |  |

|                 |            |                  | Driver enable control, pulled down internally:                                   |  |  |  |

| DE              | 3          | Digital Input    | 1. When DE is high, driver is enabled;                                           |  |  |  |

|                 |            |                  | 2. When DE is low or open, driver is disabled.                                   |  |  |  |

| DI              | 4          | Digital Input    | Driver data input, pulled up internally.                                         |  |  |  |

| GND             | 5          | Ground           | Ground.                                                                          |  |  |  |

| A               | 6          | Bus Input/Output | Noninverting driver output/receiver input.                                       |  |  |  |

| В               | 7          | Bus Input/Output | Inverting driver output/receiver input.                                          |  |  |  |

| N               | 8          | Dowor            | Power supply input, bypass $V_{CC}$ to GND with $0.1\mu F$ and at least $1\mu F$ |  |  |  |

| V <sub>cc</sub> | ŏ          | Power            | capacitors as close as possible to the device.                                   |  |  |  |

|                 |            | e                |                                                                                  |  |  |  |

#### 7 Specifications

#### 7.1 Absolute Maximum Ratings<sup>1</sup>

|                  | PARAMETER                               | MIN  | MAX                                | UNIT |

|------------------|-----------------------------------------|------|------------------------------------|------|

| V <sub>CC</sub>  | Supply voltage <sup>2</sup>             | -0.5 | 7                                  | V    |

| V <sub>IO</sub>  | Bus voltage of A and B <sup>2</sup>     | -65  | 65                                 | V    |

| V <sub>IO</sub>  | Input logical voltage of DI, DE and POL | -0.3 | V <sub>CC</sub> + 0.3 <sup>3</sup> | V    |

| V <sub>IO</sub>  | Output logical voltage of RO            | -0.3 | V <sub>CC</sub> + 0.3 <sup>3</sup> | V    |

| Tj               | Junction Temperature                    |      | 150                                | °C   |

| T <sub>STG</sub> | Storage Temperature                     | -65  | 150                                | °C   |

|                  |                                         |      |                                    |      |

NOTE:

- 1. Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- 2. All voltage values are with respect to the ground terminal and are peak voltage values.

- 3. Maximum voltage must not exceed 7V.

#### 7.2 ESD Ratings

|                                          |                                                            |                 | VALUE | UNIT |

|------------------------------------------|------------------------------------------------------------|-----------------|-------|------|

|                                          | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001         | Bus pins to GND | ±30   |      |

|                                          | Human body model (HBM), per ANSI/ESDA/JEDEC 35-001         | All other pins  | ±4    | kV   |

| V <sub>ESD</sub> Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22 | -C101, all pins | ±2    |      |

|                                          | Contact discharge, per IEC 61000-4-2                       |                 | ±6    | kV   |

#### 7.3 Recommended Operating Conditions

|                   | PARAMETER                                  | MIN | NOM | MAX             | UNIT |

|-------------------|--------------------------------------------|-----|-----|-----------------|------|

| Vcc               | Supply voltage, with respect to GND        | 3.0 | 5.0 | 5.5             | V    |

| V <sub>IN</sub>   | Bus input voltage                          | -40 | ~   | 40              | V    |

| V <sub>IH</sub>   | High-level input voltage of DI, DE and POL | 2.0 | AV- | V <sub>cc</sub> | V    |

| VIL               | Low-level input voltage of DI, DE and POL  | 0   |     | 0.8             | V    |

| RL                | Differential load resistance               | 54  |     |                 | Ω    |

| 1/t <sub>UI</sub> | Data Rate                                  |     |     | 2               | Mbps |

| T <sub>A</sub>    | Ambient Temperature                        | -40 |     | 125             | °C   |

| Tj                | Junction Temperature                       | -40 |     | 150             | °C   |

#### 7.4 Thermal Information

|                  | THERMAL METRIC                         | SOIC8 (S) | UNIT |

|------------------|----------------------------------------|-----------|------|

| R <sub>θJA</sub> | Junction-to-ambient thermal resistance | 120       | °C/W |

#### CA-IF4988S

#### Version 1.00

#### Shanghai Chipanalog Microelectronics Co., Ltd.

#### 7.5 Electrical Characteristics

Over recommended operating temperature range (unless otherwise noted). All typical specifications are at  $T_A = 25^{\circ}C$  and  $V_{CC} = 5V$ .

|                               | PARAMETER                                                                                     | TEST CONDITI                                                            | ONS                  | MIN                   | ТҮР                    | MAX             | UNI |

|-------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------|-----------------------|------------------------|-----------------|-----|

| Driver                        |                                                                                               |                                                                         |                      |                       |                        |                 |     |

|                               |                                                                                               | $R_L = 60\Omega, -40V \le V_{test} \le 40V$                             | /, see Figure 8-1    | 1.2                   | 2.8                    |                 | V   |

|                               |                                                                                               | $R_L = 60\Omega$ , $-40V \le V_{test} \le 40V$ , $4.5V \le Vcc$         |                      | 2                     | 2.8                    |                 | v   |

| V <sub>OD</sub>               | Differential output voltage                                                                   | ≤ 5.5V, see Figure 8-1                                                  |                      | Z                     | 2.0                    |                 | v   |

|                               |                                                                                               | $R_L = 100\Omega$ , $C_L = 50pF$ , see Figure 8-2                       |                      | 1.7                   | 3.5                    |                 | V   |

|                               |                                                                                               | $R_L = 54\Omega$ , $C_L = 50pF$ , see Fig                               | ure 8-2              | 1.2                   | 2.8                    |                 | V   |

| $\Delta  V_{OD} $             | Change in magnitude of<br>differential-output voltage                                         | R <sub>L</sub> = 100Ω or 54Ω, C <sub>L</sub> = 50pF, see Figure 8-2     |                      | -200                  |                        | 200             | m∖  |

| V <sub>oc</sub>               | Common-mode output voltage                                                                    |                                                                         |                      | 1                     |                        | 3.2             | V   |

| ΔV <sub>OC(SS)</sub>          | Change in magnitude of steady-<br>state common-mode output<br>voltage                         | - κ <sub>L</sub> = 100Ω 01 54Ω, c <sub>L</sub> = 50β                    | r, see Figure 8-2    | -100                  |                        | 100             | m∖  |

| I <sub>OSD</sub>              | Driver short-circuit output current                                                           | DE = $V_{CC}$ , $-65V \le V_0 \le 65V^1$ , or A pin shorted<br>to B pin |                      | -200                  |                        | 200             | mA  |

| Receiver                      |                                                                                               |                                                                         |                      |                       |                        |                 |     |

|                               |                                                                                               |                                                                         | V <sub>I</sub> = 12V |                       |                        | 125             |     |

|                               |                                                                                               |                                                                         | $V_1 = -7V$          | -100                  |                        |                 |     |

| I,                            | Bus input current                                                                             | DE = 0V, $V_{cc}$ = 0V or 5.5V                                          | V <sub>I</sub> = 40V |                       |                        | 410             | μA  |

|                               |                                                                                               |                                                                         | $V_{I} = -40V$       | -400                  |                        |                 | 1   |

| Rı                            | Bus input resistance                                                                          | Over V <sub>CM</sub> range                                              |                      | 96                    |                        |                 | kΩ  |

| V                             | Common mode veltage range                                                                     | 3V ≤ Vcc ≤ 3.6V                                                         |                      | -25 25                |                        | 25              | v   |

| V <sub>CM</sub>               | Common mode voltage range                                                                     | $4.5V \le Vcc \le 5.5V$                                                 |                      | -40 40                |                        |                 | v   |

| V <sub>TH+</sub>              | Positive-going receiver differential-<br>input voltage threshold                              |                                                                         |                      | 4                     |                        | -20             | m۱  |

| V <sub>TH-</sub>              | Negative-going receiver<br>differential-input voltage<br>threshold                            | Over $V_{CM}$ range, POL = 0V,                                          | see Table 9-2        | -200                  | 8P.                    |                 | m∖  |

| V <sub>HYS</sub> <sup>2</sup> | Receiver differential-input voltage threshold hysteresis, V <sub>TH+</sub> – V <sub>TH-</sub> |                                                                         | (                    | 2                     | 30                     |                 | m\  |

| V <sub>OH</sub>               | High-level output voltage                                                                     | I <sub>OH</sub> = –3mA                                                  |                      | V <sub>CC</sub> – 0.4 | V <sub>CC</sub> – 0.25 |                 | V   |

| Vol                           | Low-level output voltage                                                                      | I <sub>OL</sub> = 3mA                                                   | (                    |                       | 0.2                    | 0.4             | V   |

| I <sub>OSR</sub>              | Receiver short-circuit output<br>current                                                      | POL = DE = 0V, see Figure 8                                             | 3-3                  |                       |                        | 95              | mA  |

| Input Lo                      | gic (DI, DE, POL)                                                                             |                                                                         |                      |                       |                        |                 |     |

| I <sub>IN</sub>               | Input Current                                                                                 | $0V \le V_{IN} \le V_{CC}$ ,<br>after hot-swap protection               | delay for DE         | -10                   |                        | 10              | μA  |

| VIH                           | High-level input voltage                                                                      |                                                                         |                      | 2.0                   |                        | V <sub>CC</sub> | V   |

| VIL                           | Low-level input voltage                                                                       |                                                                         |                      | 0                     |                        | 0.8             | V   |

| Supply                        |                                                                                               |                                                                         |                      |                       |                        |                 | L   |

| I <sub>cc</sub>               | Quiescent supply current                                                                      | DE = V <sub>CC</sub> , empty load, no sv                                | witching             |                       | 2.2                    | 3.5             | m/  |

| TSD                           | Thermal shutdown threshold                                                                    |                                                                         | -                    |                       | 185                    |                 | °C  |

|                               | Thermal shutdown hysteresis                                                                   |                                                                         |                      |                       | 20                     |                 | °C  |

1. In the case of high ambient temperature, when pin A or pin B applies a voltage with a high absolute value, overtemperature protection may be triggered. At this time, the driver outputs become high-impedance, and the short-circuit output current would be greatly reduced.

2. Under any specific conditions,  $V_{TH+}$  is specified to be at least  $V_{HYS}$  higher than  $V_{IT-}$ .

#### 7.6 Timing Characteristics

Over recommended operating temperature range (unless otherwise noted). All typical specifications are at T<sub>A</sub> = 25°C and V<sub>CC</sub> = 5V.

|                                          | PARAMETER                                                   | TEST CONDITIONS                                     | MIN | ТҮР | MAX | UNIT |

|------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------|-----|-----|-----|------|

| Driver                                   |                                                             |                                                     |     |     |     |      |

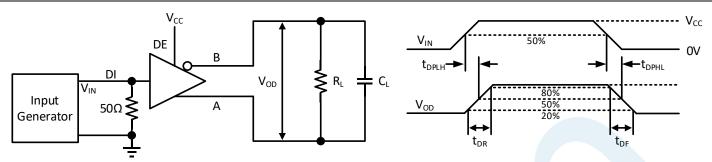

| t <sub>DR</sub> , t <sub>DF</sub>        | Differential output rise and fall time                      |                                                     |     | 55  | 200 | ns   |

| t <sub>dphl</sub> ,<br>t <sub>dplh</sub> | Driver propagation delay                                    | $R_L = 54\Omega$ , $C_L = 50pF$ , see Figure 8-4    |     | 80  | 250 | ns   |

| t <sub>DSKEW</sub>                       | Driver pulse skew,  t <sub>DPHL</sub> – t <sub>DPLH</sub>   | ]                                                   |     | 1   | 100 | ns   |

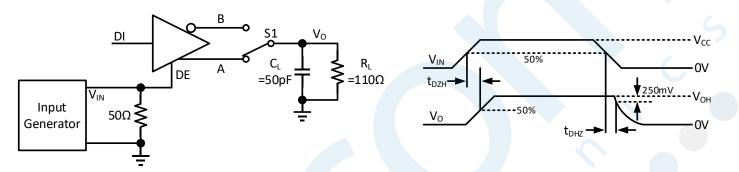

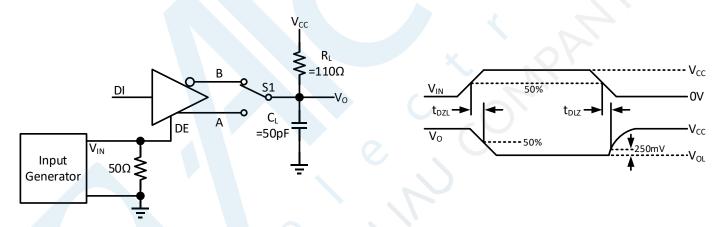

| t <sub>DHZ</sub> ,<br>t <sub>DLZ</sub>   | Driver disable time                                         | See Figure 8-5 and Figure 8-6                       |     | 100 | 250 | ns   |

| t <sub>DZH</sub> ,<br>t <sub>DZL</sub>   | Driver enable time                                          |                                                     |     | 110 | 450 | ns   |

| Receiver                                 | r                                                           |                                                     |     |     |     | 6    |

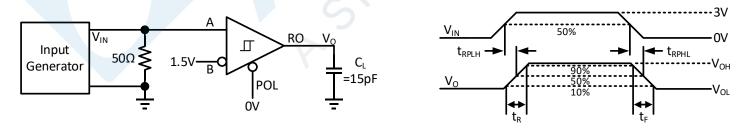

| t <sub>rphl</sub> ,<br>t <sub>rplh</sub> | Receiver propagation delay time                             | C <sub>L</sub> = 15pF <sup>1</sup> , see Figure 8-7 |     | 135 | 220 | ns   |

| t <sub>RSKEW</sub>                       | Receiver pulse skew,  t <sub>RPHL</sub> – t <sub>RPLH</sub> |                                                     |     | 1   | 30  | ns   |

| <b>NOTE:</b><br>1. C <sub>L</sub> ii     | ncludes probe and fixture capacitance.                      |                                                     |     |     | •   |      |

# CHIPANALOG

Shanghai Chipanalog Microelectronics Co., Ltd.

#### CA-IF4988S Version 1.00

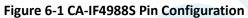

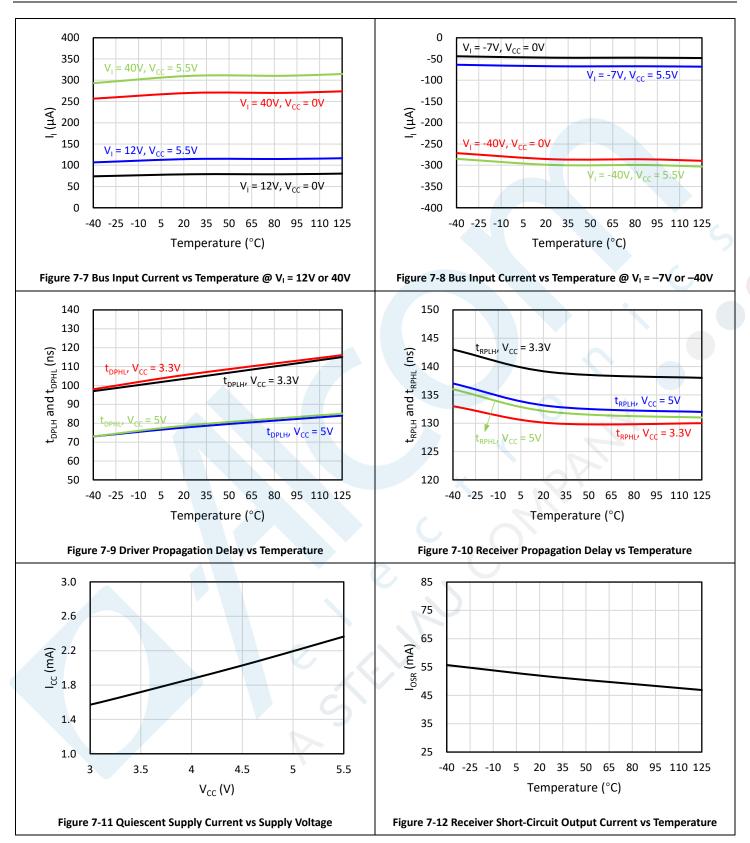

#### 7.7 Typical Characteristics

All typical specifications are at  $T_A = 25^{\circ}C$  and  $V_{CC} = 5V$  (unless otherwise noted).

Copyright © 2024, Chipanalog Incorporated 上海川土微电子有限公司

CA-IF4988S Version 1.00

Shanghai Chipanalog Microelectronics Co., Ltd.

#### 8 Parameter Measurement Information

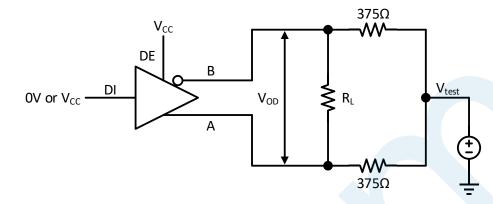

Figure 8-1 Measurement of Driver Differential Output Voltage With Common-Mode Load

Figure 8-2 Measurement of Driver Differential and Common-Mode Output Voltage With RS-485 Load

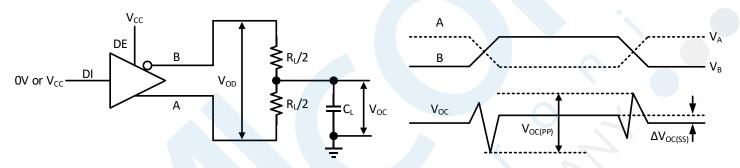

Figure 8-3 Measurement of Receiver Output Short Circuit Current

Figure 8-4 Measurement of Driver Output Rise and Fall Time and Propagation Delay

Figure 8-5 Measurement of Driver Enable and Disable Time With Active High Output and Pull-Down Load

Figure 8-6 Measurement of Driver Enable and Disable Time With Active Low Output and Pull-Up Load

Figure 8-7 Measurement of Receiver Output Rise and Fall Time and Propagation Delay

#### 9 Detailed Description

#### 9.1 Device Feature Description

#### 9.1.1 ±65V fault protection on Bus Pins

The bus pins of transceivers connected to a RS-485 network often experience faults when shorted to voltages that exceed the – 7V to 12V input range specified in the EIA/TIA-485 standard. Under such circumstances, ordinary RS-485 transceivers generally require costly external protection devices which can compromise the performance. To reduce system complexity and the requirements of external protection devices, The CA-IF4988S has ±65V fault protection on bus pins with respect to ground whenever this device is under enabled, disabled or power-down mode. When the driver is enabled and the bus pins are short-circuited, the driver would limit the output short-circuit current within a certain range by the built-in current limiter firstly. If the absolute value of the bus pin's fault voltage is large, the device's junction temperature could increase rapidly to trigger the thermal shutdown protection. Once the device's junction temperature rises above the thermal shutdown temperature, the driver would be disabled and the outputs become high-impedance, resulting in the reduction of power consumption and thus avoiding further thermal damage.

#### 9.1.2 ±40V Common-Mode Range

RS-485 standards define the common-mode range as –7V to 12V for the receiver. However, the common-mode range of the CA-IF4988S exceeds the standard with ±40V for both the driver and receiver. This feature was specifically designed for systems where there is a large common-mode voltage present due to either nearby electrically noisy equipment or large ground differences due to earth ground loop. Compared with ordinary RS-485 transceivers, ±40V common-mode range could ensure that the CA-IF4988S communicates correctly in a broader range of applications.

#### 9.1.3 Bus Failsafe Protection

The input threshold of the CA-IF4988S's receiver ranges from -20mV to -200mV when POL is held to low, which guarantees a logical high on the receiver output when the bus inputs are open, short or on idle state.

#### 9.1.4 Hot Plug-in Protection

Inserting circuit boards into a powered backplane may cause voltage transients on DE and bus input pins that can lead to data errors. For example, upon initial circuit board insertion, the processor undergoes a power-up sequence. During this period, the high-impedance state of the output drivers makes them unable to drive the DE input to a defined logic level. Meanwhile, coupling noise from  $V_{CC}$  or GND could cause the input of DE to drift to an indeterminate logic state. The internal hot plug-in protection circuit on DE pin could avoid unwanted driver activation during hot-swap situations. The basic working principle of this circuit is to strongly pull down the input of DE at least 15 $\mu$ s when detecting the rising from low voltage of the power supply. After the power-up sequence, this hot plug-in protection circuit is bypassed and DE could receive the normal control signal from outside.

#### 9.1.5 Thermal Shutdown Protection

The CA-IF4988S integrates thermal shutdown protection circuit. When the junction temperature rises above 185°C (typical value), the output of driver is disabled and the output of RO is high-impedance. When the junction temperature falls below 165°C (typical value), the output of both driver and receiver is re-enabled.

#### 9.2 Device Function Mode

#### 9.2.1 Driver

When the enable pin DE of driver is logical high, the differential outputs of A and B follow with the data input DI, as well as influenced by logical level at POL pin, which is shown in Table 9-1.

When DE is logical low or open, the driver is disabled, the outputs of A and B are high-impedance and are irrelevant to the state at DI pin. DI pin is weakly pulled up to V<sub>CC</sub> internally, the output of A is high while B is low when driver is enabled, DI's input is open and POL is logical low.

#### Table 9-1 Truth Table of Driver<sup>1</sup>

| POL <sup>2</sup>           | DE <sup>3</sup>                                                                                                        | DI <sup>4</sup> | А      | В      |  |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------|--------|--------|--|--|

| L                          | Н                                                                                                                      | L               | L      | Н      |  |  |

| L                          | Н                                                                                                                      | Н               | Н      | L      |  |  |

| Н                          | Н                                                                                                                      | Н               | L      |        |  |  |

| н н                        |                                                                                                                        | Н               | L      | Н      |  |  |

| Х                          | X L                                                                                                                    |                 | High-Z | High-Z |  |  |

| 2. POL is weakly pulled of | level, X = irrelevant, High-Z =<br>lown to GND internally.<br>own to GND internally.<br>to V <sub>cc</sub> internally. | high impedance. |        |        |  |  |

#### 9.2.2 Receiver

After V<sub>CC</sub> is powered up, the receiver is always enabled in normal operation, but would be disabled when the device triggers thermal shutdown. RO is high-impedance under thermal shutdown conditions.

The truth table of receiver is shown in Table 9-2.

When POL is logical low and the bus differential input voltage  $V_{ID}$  is greater than or equal to -20mV, receiver output RO is logical high. When  $V_{ID}$  is less than or equal to -200mV, receiver output RO is logical low. When  $V_{ID}$  is between -20mV and -200mV, receiver output RO is indeterminate.

When POL is logical high and the bus differential input voltage  $V_{ID}$  is greater than or equal to 200mV, receiver output RO is logical low. When  $V_{ID}$  is less than or equal to 20mV, receiver output RO is logical high. When  $V_{ID}$  is between 20mV and 200mV, receiver output RO is indeterminate.

When POL is logical low and the bus inputs are open, short or on idle state, a failsafe logic high output at RO pin is achieved. Under such conditions while POL is logical high, a failsafe logic low output at RO pin is achieved.

| POL                                                     | $V_{ID} = (V_A - V_B)$         | RO |  |  |  |  |

|---------------------------------------------------------|--------------------------------|----|--|--|--|--|

|                                                         | ≥ –20mV                        | Н  |  |  |  |  |

| L                                                       | $-200 mV < V_{ID} < -20 mV$    | ?  |  |  |  |  |

|                                                         | ≤ –200mV                       | L  |  |  |  |  |

|                                                         | ≤ 20mV                         | Н  |  |  |  |  |

| Н                                                       | 20mV < V <sub>ID</sub> < 200mV | ?  |  |  |  |  |

|                                                         | ≥ 200mV                        | L  |  |  |  |  |

| L                                                       | Open/Short/Idle                | Н  |  |  |  |  |

| Н                                                       | Open/Short/Idle                | L  |  |  |  |  |

| NOTE: H = high level, L = low level, ? = indeterminate. |                                |    |  |  |  |  |

#### Table 9-2 Truth Table of Receiver

### CA-IF4988S

Version 1.00

#### Shanghai Chipanalog Microelectronics Co., Ltd.

#### 10 Application and Implementation

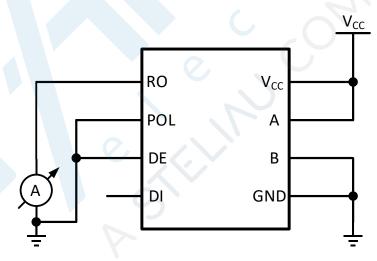

#### **10.1** Typical Application

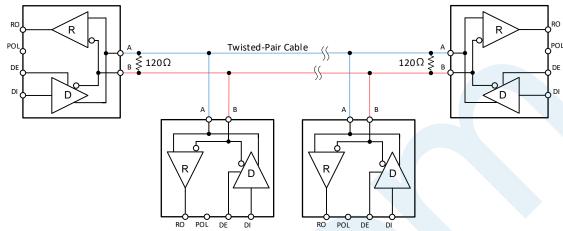

Figure 10-1 Typical RS-485 Network

The typical RS-485 network consists of multiple transceivers connecting in parallel to a bus cable. To eliminate the line reflection, both ends of the cable terminate a termination resistor  $R_T$  which should be matched to the characteristic impedance  $Z_0$  of the cable. At the same time, please keep the stub lengths off the main line as short as possible. This parallel termination method could achieve higher data rates over longer cable length. The typical RS-485 network utilizing CA-IF4988S is shown in Figure 10-1.

If certain node's transceiver is cross-wired in field cables which results in inverting bus polarity, it could be corrected to set POL to high by controller allowing for software correction.

#### 10.2 Power Supply Recommendation

To ensure reliable operation at all data rates and supply voltages, each supply should be decoupled with  $0.1\mu$ F and at least  $1\mu$ F ceramic capacitors located as close as possible to the supply pins. This helps to reduce supply voltage ripple present on the outputs of switched-mode power supplies and also helps to compensate for the resistance and inductance of the PCB power planes. At the same time, please keep the voltage in V<sub>cc</sub> pin with respect to GND pin is below 5.5V.

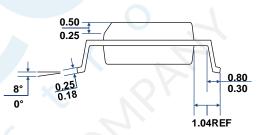

#### 11 Package Information

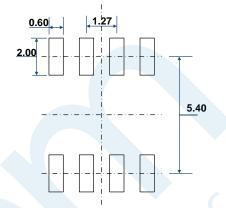

#### 11.1 SOIC8 (S) Package

The values for the dimensions are shown in millimeters.

# **RECOMMENDED LAND PATTERN**

## **LEFT-SIDE VIEW**

FRONT VIEW

CHIPANA Shanghai Chipanalog Microelectronics Co., Ltd.

.0G

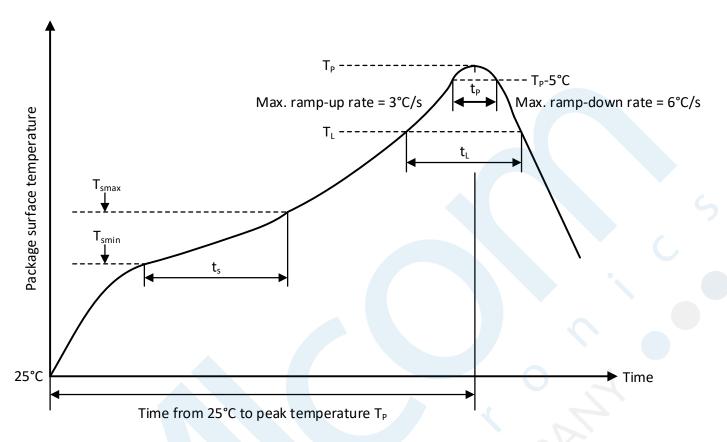

#### 12 Soldering Information

| Table 12-1 Soldering Temperature Parameters | Table 12-1 | Soldering | Temperature | <b>Parameters</b> |

|---------------------------------------------|------------|-----------|-------------|-------------------|

|---------------------------------------------|------------|-----------|-------------|-------------------|

| Profile Feature                                                                       | Pb-Free Soldering |  |  |  |  |

|---------------------------------------------------------------------------------------|-------------------|--|--|--|--|

| Ramp-up rate ( $T_L$ = 217°C to peak $T_P$ )                                          | 3°C/s max         |  |  |  |  |

| Time $t_s$ of preheat temp ( $T_{smin} = 150^{\circ}C$ to $T_{smax} = 200^{\circ}C$ ) | 60~120 seconds    |  |  |  |  |

| Time $t_L$ to be maintained above 217°C                                               | 60~150 seconds    |  |  |  |  |

| Peak temperature T <sub>P</sub>                                                       | 260°C             |  |  |  |  |

| Time t <sub>P</sub> within 5°C of actual peak temp                                    | 30 seconds max    |  |  |  |  |

| Ramp-down rate (peak $T_P$ to $T_L = 217^{\circ}C$ )                                  | 6°C/s max         |  |  |  |  |

| Time from 25°C to peak temperature T <sub>P</sub>                                     | 8 minutes max     |  |  |  |  |

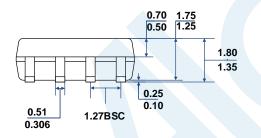

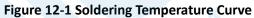

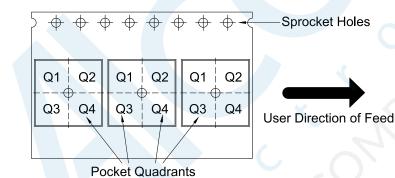

#### **13** Tape and Reel Information

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device     | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| CA-IF4988S | SOIC            | S                  | 8    | 2500 | 330                      | 12.4                     | 6.5        | 5.4        | 2.1        | 8.0        | 12.0      | Q1               |

#### CA-IF4988S Version 1.00

#### Shanghai Chipanalog Microelectronics Co., Ltd.

#### 14 Important Notice

The above information is for reference only and is used to assist Chipanalog customers in design and development. Chipanalog reserves the right to change the above information due to technological innovation without prior notice.

Chipanalog products are all factory tested. The customers shall be responsible for self-assessment and determine whether it is applicable for their specific application. Chipanalog's authorization to use the resources is limited to the development of related applications that the Chipanalog products involved in. In addition, the resources shall not be copied or displayed. And Chipanalog shall not be liable for any claim, cost, and loss arising from the use of the resources.

#### **Trademark Information**

Chipanalog Inc. <sup>®</sup>, Chipanalog<sup>®</sup> are trademarks or registered trademarks of Chipanalog.

Singel 3 | B-2550 Kontich | Belgium | Tel. +32 (0)3 458 30 33 | info@alcom.be | www.alcom.be Rivium 1e straat 52 | 2909 LE Capelle aan den Ijssel | The Netherlands | Tel. +31 (0)10 288 25 00 | info@alcom.nl | www.alcom.nl